特点,互相关值很小。由上式可见,第二项是影响误判的主要因素,此处对于误码率的讨论不同于一般意义的QPSK+扩频方式,因此将采用仿真的方式对误码率进行讨论。

利用计算机仿真,可得到高斯噪声下的误码率曲线如图2 所示。从仿真结果看,当SNR ≥- 20 dB 时,满足语音通信(BER ≤10-3 ) 的要求;当SNR ≥- 14 dB 时,满足数据通信(BER ≤10-6 ) 的要求。

图2 高斯信道的误码性能

算法在DSP+FPGA 系统中的实现

由于数字相关模块主要由FPGA 和DSP 来完成,因此主要的算法将嵌入进这两个芯片中。

DSP+FPGA 系统的最大优点是结构灵活,有较强的通用性,适合于模块化设计,从而能够提高算法效率;同时其开发周期较短,系统容易维护和扩展,适合实时信号处理。

实时信号处理系统中,低层的信号预处理的数据量大,对处理速度的要求高,但运算结构相对比较简单,适用于FPGA 执行硬件实现,这样能同时兼顾速度和灵活性。高层处理算法的特点是所处理的数据量较低层算法少,但算法的控制结构复杂,适用于运算速度高、寻址方式灵活、选用通信机制强大的DSP 芯片来实现。

DSP+FPGA 系统的核心由DSP 芯片和可重构器件FPGA 组成。另外还包括一些外围的辅助电路,如存储器、先进先出( FIFO) 器件及FLASH ROM 等。FPGA 电路与DSP 相连,利用DSP 处理器强大的I/O 功能实现系统内部的通信。从DSP 角度看,FPGA 相当于他的宏功能协处理器。外围电路辅助核心电路进行工作。DSP 和FPGA 各自带有RAM ,用于存放处理过程所需要的数据及中间结果。FLASH ROM 中存储了DSP 执行程序和FPGA 的配置数据。先进先出( FIFO) 器件则用于实现信号处理中常用到的一些操作,如延迟线、顺序存储等。

在本系统的设计中,DSP 采用TI 公司的C5409A ,同时采用SPANSION 公司的AM29LV200BT 作为DSP 的外挂FLASH ,存放相应的程序; FPGA 采用的是Xilinx 公司的XCV600E ,同时采用Xilinx 公司的XC18V00 作为专用配置芯片,存放FPGA 程序;在FPGA 中将进行FIFO 的设计,DSP 通过对FIFO 的读取来实现两块芯片间的通信。

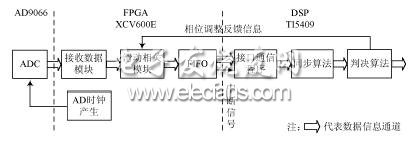

总体的算法分为FPGA 和DSP 部分: FPGA 的算法主要包含的功能是,产生AD 采样时钟,接收AD 数据,滑动相关,FIFO 构成及DSP 中断产生;DSP 含有:同步算法,判决算法。

以下是算法在各芯片中的嵌入分配示意图,如图3所示。

图3 算法在各芯片中的嵌入示意图

FPGA 和DSP 两部分的算法必须协同运行,他们之间的关系是:FPGA 的算法由时钟来驱动,每个时钟到来时,他都要进行相应的数据接收,滑动相关,将相关值推入FIFO 的操作,当他将FIFO 置到一定程度时,则向DSP 发中断信号;DSP 的程序在大部分时间处于一种循环等待的状态,而他一收到FPGA 的中断,则进行响应,先将FIFO 里面的若干数据读出,然后进行相应的中断处理,由DSP 完成同步处理,相关判决并实现基带通信。总的流程图如图4 所示。

系统的运行的实测性能

正常通信时,误码率稳定在1*10-5 。高斯噪声干扰(未解扩解调前加干扰) ,语音信号正常通信(误码率≤1×10-3 ) 的信干比:-17dB。在抗干扰方面,对于非瞄准式单频干扰语音信号的正常通信(误码率≤1×10-3 ) 的信干比:-14~-2dB(随频点有差异) ;而对于瞄准式单频干扰当达到- 12 dB 时,仍能继续保持语音通信。

图4 FPGA 及DSP 流程图