4.1 处理器模块

处理器型号的选择关系到定位节点的工作性能。

ATmega644v单片机是一款高性能、低功耗、采用精简指令集结构、具有64 K在线可编程存储器、2 K的EEPROM、4 K的内部SRAM。单片机具有JTAG接口、串行通信口和SPI接口。

ATmega644v单片机采用CMOS工艺,基于AVR增强精简指令集结构的8位微处理器。一个时钟周期执行一条指令,指令执行速度达到1MIP-S。AVR内核包含丰富的指令集和32个通用的工作寄存器,通用寄存器直接与算术逻辑单元相连,允许两个独立的寄存器在一个指令周期内同时访问。采用精简指令集结构的AVR单片机比传统的采用复杂指令集结构的单片机执行代码的速度快10倍。

单片机通过SPI接口控制NA5TR1工作,端口9和端口10为通用串口,可以直接与外部串口线相连实现串口通信,也可以与USB转串口的CH341T的输出口相连。

4.2 通信模块

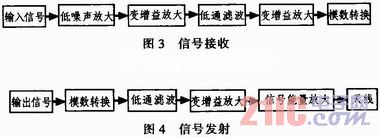

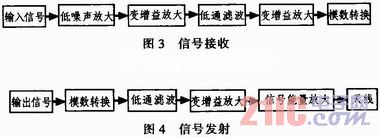

NA5TR1提供3个可自由调整中心频率的非重叠2.4GHzISM频道,支持多个独立物理层网络,并能够提高与现有2.4GHz无线技术共存时的网络性能。数据通讯速率为125 kb/s~2 Mb/s可选。由于芯片采用独特的窄脉冲扩频技术天线的调试要求并不十分严格,这大大简化了系统安装和维护的复杂度,并能够做到随拿随放。包含一个性能卓越的MAC控制器,提供对载波侦听、多路访问/冲突避免(CSMA/CA)和时分多址接入(TDMA)协议的支持,并实现前向纠错(FEC)和128位硬件加密。为了降低对微控制器和软件的要求,NA5TR1芯片同时提供不规则的自动地址匹配及数据包重发功能。NA5TR1 TRX无线收发器集成了数字色散延迟线(DDDL),它负责接收并区分其他NA5TR1收发机发出的两种信号。接收到的信号可能是Up Chirp、Down Chirp中的一种,或者是一个交叠信号(Up Chirp、Down Chirp同时出现的混合信号),且所有的这些信号具有相同的中心频率和带宽。Up Chirp信号和Down Chirp信号的区别,仅表现在复杂频谱的相位信息中。这个相位信息足以被数字色散延迟线(DDDL)用来在输出口压缩脉冲并在另一端展开(也就是说,将接收到的信号展开到双倍持续时间)。通过这种方式,数字色散延迟线(DDDL)作为匹配滤波器过滤传输脉冲,芯片内部数据传输过程如图3信号接收,图4信号发射。

4.3 电源模块

NA5TR1芯片内部分成数字部分和模拟部分,数字部分提供控制芯片的可编程的接口和数字缓冲区,数字缓冲区用来存放要发送的数据和接收的数据。模拟部分将数字信号转换成模拟尖脉冲用来发送和将接收到的尖脉冲转换成数字信号。模拟部分只能通过数字部分进行访问。

为了最大限度的节能,数字部分分成了两部分,始终上电的部分和需要运行的时候才上电的部分,始终上电的部分包括需要控制的最小数字部分,用来维持芯片的设置。此部分与I/O口连接,这些接口控制电源管理器。不始终上电的部分包含了控制数据的发送和接收的部分,只有需要的时候才上电,以达到芯片最大限度的节能。

4.4 设计注意事项

无线定位节点的设计要求定位精度越高越好,体积越小越好,NA5TR1集成度高、外部电路简单,合理布局电源管脚去耦电容,使用0403电容封装可以满足要求。由于芯片工作的频率比较高,提高定位节点的抗干扰性是设计PCB板的关键,设计PCB板时可以采用多层板,第一层为信号层,第二层为接地层,第三层为电源层,第四层为信号层,利用第二层接地层的屏蔽效应达到射频信号的高质量传输。在板子信号层的空白地方敷铜接地,减少信号线之间的干扰。

为了达到输出信号最强,需要在平衡变压器输出到天线之间的信号线进行阻抗匹配50Ω,信号传输中没有信号反射产生,这样就使得到达天线的信号最强。输出阻抗与制作PCB的板材、线宽、层间距都有关系。所以在制作PCB时,应该向厂家说明输出部分线路的阻抗匹配要求,由厂家来完成设计和计算,以确保最终的电路板能够符合阻抗匹配要求。通常无线射频电路要求板材的介电常数越小越稳定越好。介电常数越小,层间的电子移动越少,射频信号的泄漏也会越小,射频信号在板上的损失就越小。

5 结束语

近年来随着无线通信技术的发展,无线定位节点的设计成本不断降低,无线定位技术的使用领域也不断扩大。短距离、低功耗、低成本的窄脉冲扩频技术的提出及应用,使得无线定位节点的定位精度及抗干扰性有了很大的改善。尤其是其独特的测距功能,叮满足不同行业的应用要求,基于该芯片的无线定位节点设计方案有很好的应用前景。

上一页 [1] [2] [3]