2 虚拟示波器SOPC系统构建及NiosⅡ软件开发

2.1 虚拟示波器SOPC系统构建

本文采用ALTERA公司的NiosⅡ软核处理器,并利用FPGA设计虚拟示波器系统。ALTERA 公司的NiosⅡ软核处理器是一个32位RISC嵌入式处理器,具有5级流水线、采用数据和指令分离的Harvard结构、提供众多标准外设和软件集成开发环境。

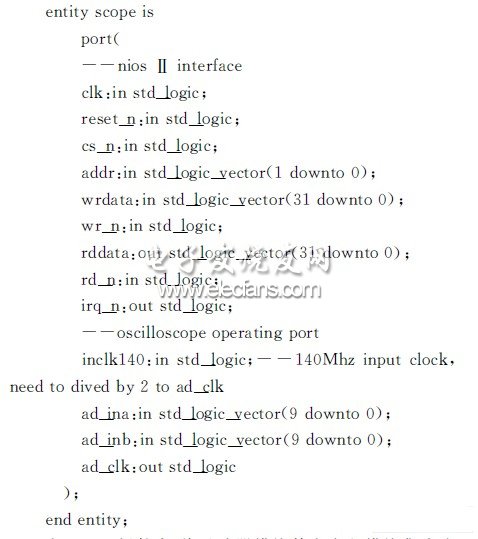

进行基于Nios Ⅱ 的SOPC 系统开发时,可利用ALTERA提供的SOPC插件,进行外设和CPU的配置,并提供自定义IP的构建方法。在虚拟示波器系统中,需要开发符合AVALON总线的示波器模块,并加入到自定义IP中。示波器模块实体程序如下:

在SOPC插件中,将示波器模块等自定义模块集成为IP核,分别将NiosⅡJTAG_UART、FLASH以及SRAM等IP核加入虚拟示波器系统中,SOPC系统配置图如图5所示。

配置完成后,生成系统,并在QuartusⅡ中进行引脚配置,然后综合、布线,生成配置文件,通过JTAG 对FPGA进行配置,即可获得虚拟示波器系统的信息处理部分硬件电路。

2.2 NiosⅡ软件开发

实践证明,当系统的复杂程度达到一定时,采用嵌入式操作系统不仅会简化程序员工作、提高CPU利用率,而且会提高系统可靠性。因此本系统的下位机软件采用嵌入式操作系统。mICroc/os-Ⅱ是1个性能优良的嵌入式多任务实时操作系统,稳定度高、安全性好;同时NiosⅡ开发环境中集成了性能良好的、免费的microc/os-Ⅱ估算版,因此虚拟示波器系统采用该操作系统。

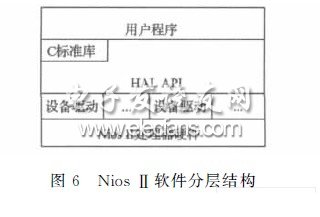

NiosⅡ的软件开发一般采用分层的方式进行,它采用类似Linux的设备文件系统来管理设备,采用HAL(硬件抽象层)完成硬件相关设备的封装操作,因此每个CPU外设都需要有相应的驱动程序。虚拟示波器系统中,NiosⅡ的驱动分层结构如图6所示。

虚拟示波器系统需要为定义的IP设计相应的驱动程序,对于最底层与硬件相关的操作,NiosⅡ提供了IOWR(base,offerset,data)和IORD(base,offerset)2个宏,分别用于对寄存器的读、写操作。这里,base为虚拟示波器驱动程序的基地址,其自动生成;offerset为指被操作的寄存器在该设备中的偏移地址。

2.3 嵌入式USB协议栈开发

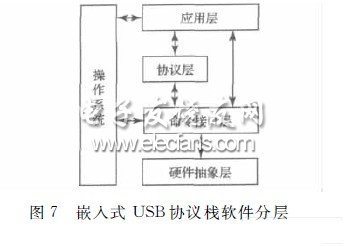

USB协议复杂,虚拟示波器系统开发的USB协议栈基于microc/os-Ⅱ,并采用了如图7的分层结构,以减少开发调试的难度。

硬件抽象层和命令接口层都与硬件相关,硬件抽象层负责对SX2的寄存器进行读写操作,而命令接口则实现与SX2的工作方式有关的操作;协议层与平台无关,其主要完成USB的枚举及各端口数据处理;应用层完成对提供调用的函数进行封装,应用层提供了简单的API接口,其利用senddata函数发送数据到主机,同时利用recdata函数从主机接收数据以及厂商请求的函数,上层程序只要简单地调试这3个函数而无需关注USB协议,即可完成虚拟示波器的USB通信。