控制系统组成及工作特点

1、控制系统组成

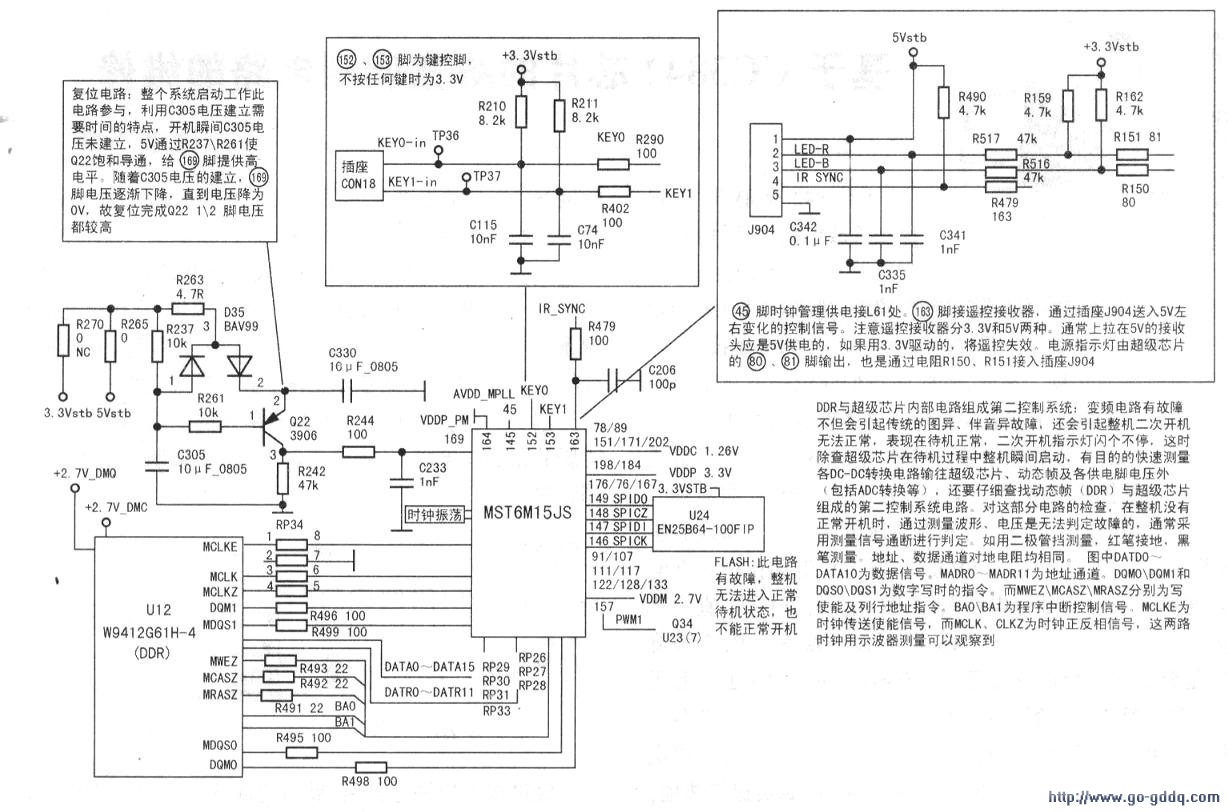

此机芯控制系统与传统CRT电视、高清电视有较大差异,控制系统分两部分:第一部分由通常在平板电视上都能见到的由时钟振荡、复位电路、FLASH、E2PROM和超级芯片组成(注:FLASH即闪存是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。任何FLASH器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。如果需要改写只需特殊的工具和按操作程序即可对FLASH块进行程序重新写入,这样的过程一般维修人员都可以掌握操作,不像以往的CRT电视程序由整机公司才能进行而且不能改写,一旦控制系统损坏,就只有替换整个带有CPU功能的CPU,如TDA9370类的超级芯片);另一控制系统是在第一控制系统工作后,在待机过程中同时启动与第一控制系统有关的程序单元,并同时启动第二控制系统,将第一控制系统指挥整机工作的程序调入第二控制系统。第二控制系统由超级芯片和DDR存储器组成。DDR存储器其实就是原来的动态帧存储器。原来的动态帧存储器常叫作SDRAM存储器,现在叫DDRSDRAM存储器,这两种存储器的区别在于后者是同步双数据速率的SDRAM存储器,它是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系。该机第二控制系统由MST6M15JS(86)—(139)脚与FLASH块.DDR存储器U12(HY5DU281622ET-4)组成。

2.整个控制系统的工作过程

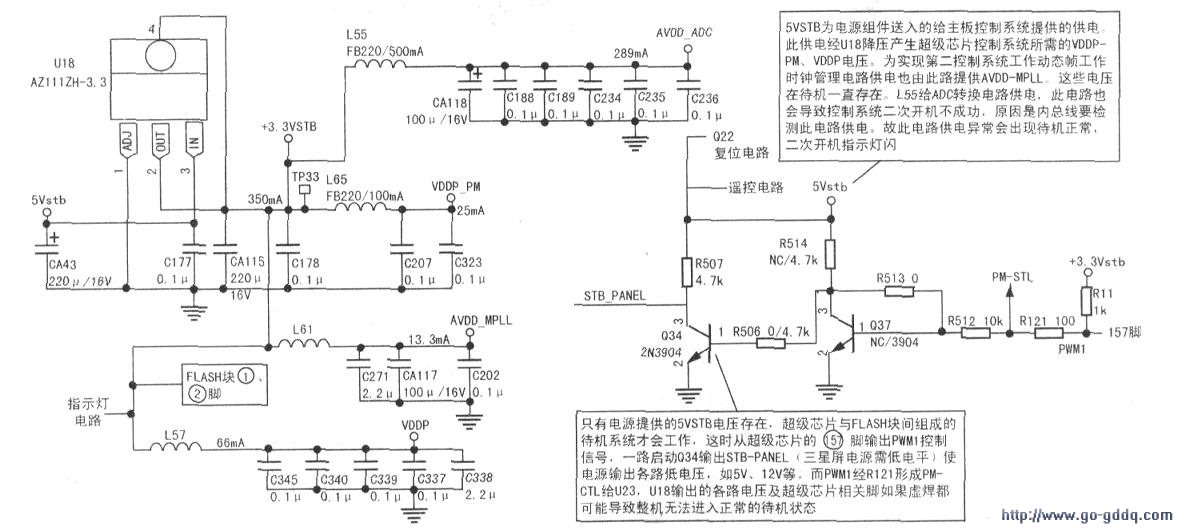

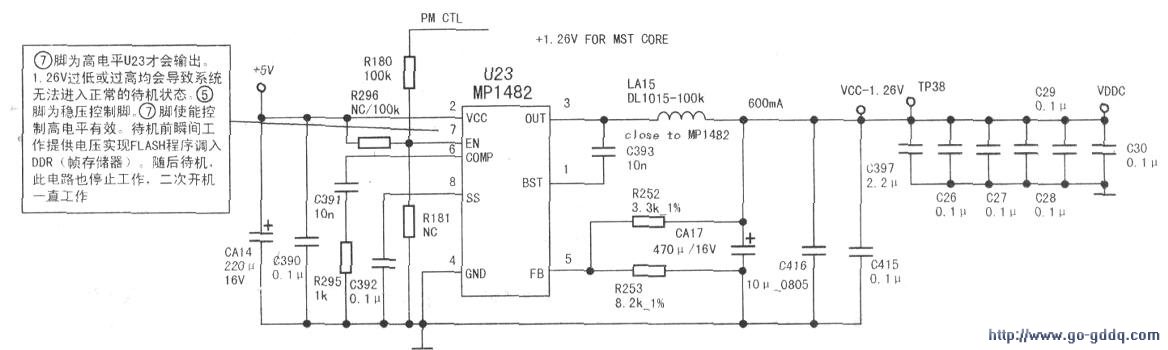

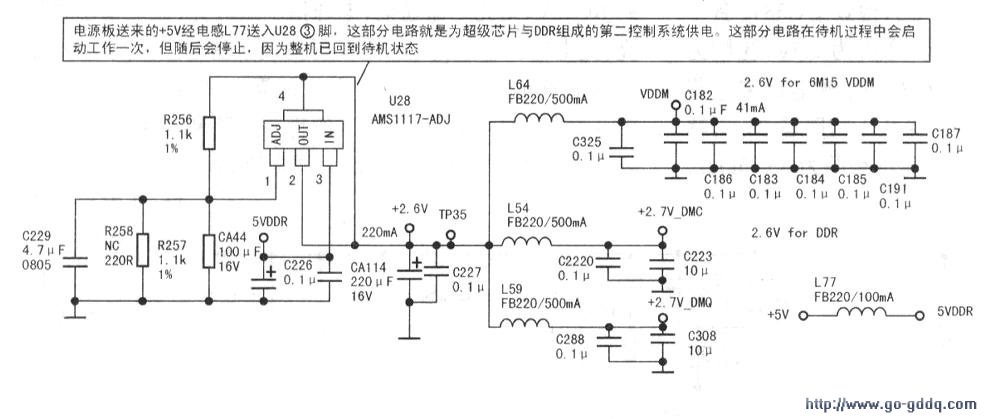

交流电接通后,由电源组件提供5VSTB给主板的遥控、复位电路,同时通过U18(见上图)形成3.3VSTB经电感L65给超级芯片(165)、(145)脚提供VDDP_PM电压(VDDP-PM,控制系统供电)和FLASH块3.3VSTB工作电压,这样超级芯片与FLASH块组成的控制系统中待机部分电路开始工作,待机控制部分电路工作后,第一控制系统中待机系统将快速启动超级芯片(157)脚输出高电平通过Q34输出转换成低电平STB-PANEL启动电源组件输出各路低电压给主板(插座JP01脚上标的SV,F-12V)。同时3.3VSTB通过电感L61给肘钟管理MPLL电路供电,这样主板的FLASH块、动态帧存储器等电路运行时钟才具备。时钟管理MPLL供电异常会导致待机不正常。上图PWM1经电阻R121后的PM-CTR接入中图所示的U23(7)脚,插座JP01(5)、(6)脚的D5V接入主板U23(2)脚,U23(7)脚得到使能高电平信号,U23工作输出1.26V供超级芯片与FLASH块间组成的程序单元电路工作。此l.26V即VDDC(给控制系统机芯供电)经LA15给超级芯片(78)、(89)等脚供电,见中下图。这样由超级芯片与FLASH块组成的程序块在U23输出电压正常的情况下开始运行;同时低电压D5V还经电感L77给U28供电使其输出+2.6V电压,见下图。此2.6V电压经电感L64形成VDDM电压给超级芯片的(91)、(107)、(111)、(117)、(122)、(128)、(133))脚内电路供电。动态帧存储器组成的第二控制系统得电,在时钟管理下开始工作,这时通过变频电路中的地址、数据、指令通道将FLASH块中程序调入DDR帧存储器预留的RAM存储空间中(见中下图申的DDR部分),实现整机控制,启动U23、U28和DDR变频电路进入工作状态,实现快速将第一控制系统的控制权交给第二控制系统。两控制系统权力交接过程是短暂的,正常情况下,在接通交流电的瞬间能观察到电源指示灯闪烁两次后常亮,再执行二次开机指示灯又会闪烁两次红色,一次绿色。待机时指示灯能闪烁表明FLASH块、U18、U23、复位电路、时钟振荡电路已能工作。执行二次开机却不能正常开机时,故障可能在U18、U28、超级芯片与DDR组成的程序交换电路中。这时应查超级芯片与动态帧存储器组成的第二控制系统相关电路,如U18输出各路电压未送入超级芯片或DDR存储器并行总线传送通道有故障等。

电视机进入待机状态后,超级芯片(157)脚输出低电平,这时主板除5VSTB、3.3VSTB电压和FLASH块中的待机部分电路工作外,其他如U23、U28及所有图像电路会因供电停止而停止工作。二次开机后整机遥控、键控、整个图像处理权才交给DDR与超级芯片组成的电路。此种电路结构可快速提高整机控制速度,同时也实现了待机功耗低的环保要求,这就是采用双核控制的优势。