一、可编程逻辑器件与单片机的接口电路

在很多电路里,可编程逻辑器件需要在外部处理器如单片机的控制下工作。这时可以把PLD或FPGA器件当作普通的单片机外围电路,利用单片机的数据、地址、控制3组总线来访问它,接口电路可用PLD或FPGA内构建出的双端口RAM来充当。双端口RAM是一种数据存储电路,具有输入和输出两个端口,每个端口都有独立的数据和地址总线,对两个端口可分别进行数据读、写操作。现以Cyclone型FPGA芯片为例来设计它和外部单片机的接口。

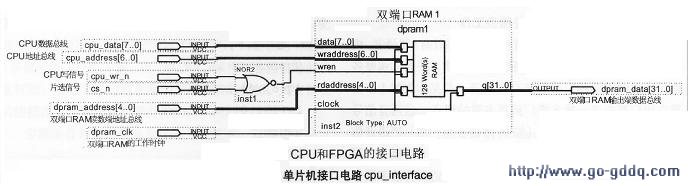

设外部单片机的数据总线cpu_data[7..0]为8位,地址总线cpUL.address[6..0]为7位,FPGA内的数据总线dpradata[31..0]选用32位,相应的地址总线dpraaddress[4.,0]就是5位。CPU选中FPGA芯片时还要有个片选信号os_n(“_n”表示低电平有效),通常由CPU的高位地址担任。因为在接下来的例子中只需要从单片机向FPGA写入控制数据,所以数据总线可简化为单向的,只用到外部CPU的写信号cpu_wr_n。

进入QUARTnsⅡ软件的功能插件管理器,选中“RA2-PORT(双端口RAM)”,按照提示一步步做下去,得到所需要的双踹口RAM,如下图中的dpraml所示。加上输出入引脚等,就设计出了下图所示的单片机接口电路。

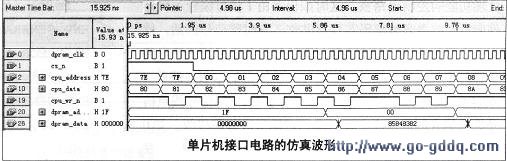

上图中,来自CPU的数据从左端输入,当CPU的写信号和片选信号都为低电平时向dprarnl写人数据。FPGA通过内部地址dpram--address[4..0]可从dpram1的右端读出数据(必要时可加上读信号)。图1中dpraⅢ-clk是Cyclone型芯片要求的双端口RAM时钟(有些类型的芯片不需要用这个时钟),由FPGA内部提供。对上图所示电路做波形仿真,结果如下图所示。

从上图可见,对外部单片机来讲,通过数据、地址、片选和写信号把数据写入FPGA与写入其他外围器件相比没有什么不同。上图中当片选和写信号都为低电平时,CPU向dpraml起始的4个外部地址处各写入1个8位数据82、83、84、85,此后从dpraml输出数据的起始地址处就可得到1个32位的数据85848382(均为16进制数),其余可类推。因为许多单片机是8位的,所以外部数据总线用8位。FPGA内部使用32位是为了提高数据处理效率。从上图所示的输出波形还可以看到,数据是按照地址大小从左到右排列的。

写入控制数据后,FPGA就能在单片机的控制下工作。

二、多片可绵程逻辑器件同步工作

此前我们所做的数字语音电路实验都只有4路语音,由PLD或FPGA为每路语音分配收/发时隙,并通过调整各路收/发时隙的相对位置来交换语音(参见本文第1节)。

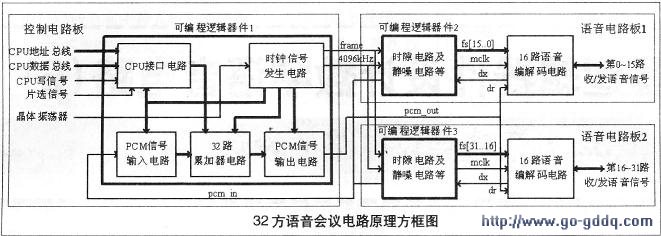

现在我们要把这一技术推广到更多路的语音。当语音信号很多时,通常按一定规律(如16路语音为一组)把语音信号的输入、输出及编解码处理电路做在一块电路板上,再把多块这样的电路板通过母线电路板连接到具有数字语音处理功能的控制电路板。这时如仍然由1块可编程逻辑器件向所有的语音编解码芯片提供收/发时隙信号的话,就需要大量的板间互连线。更合理的办法是由每块语音电路板通过本板上的可编程逻辑器件产生固定的本板各路收/发时隙,控制电路板则把来自各语音板的PCM信号按照信号的去向在时间次序上重新排列后输出供每路接收。如0号用户的收/发时隙都固定为0号时隙、1号用户的收/发时隙都固定为1号时隙,那么只要把0号时隙来的信号安排到1号时隙发回去,1号用户就收到了0号的语音。在下图所示的电路系统中,使用了2块语音电路板,每板16路语音,收/发时隙均由本板的可编程逻辑器件产生,可选用规模较小的PLD器件。控制板则集中处理和分配各路PCM语音信号,可选用资源较丰富的Cyclone器件。

由于PCM信号有严格的时序要求,语音板上编解码器的时钟必须和控制板上的时钟同步,语音板自行产生的各路时隙信号也必须在时序上和控制板保持一致。因此,控制板上的可编程逻辑器件工作于“主”模式,输出frame信号作为语音板上每帧的起始标志,输出同步的4096kHz信号作为语音板的时钟。

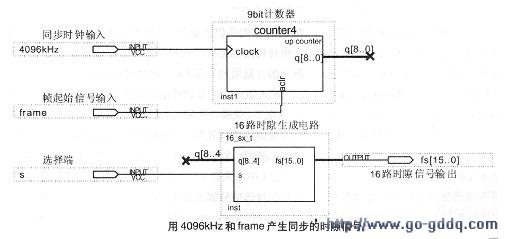

语音板则工作于“从”模式,受控于来自控制板的时钟,产生和控制板同步的时隙信号。下图所示是用PLD在“从”模式下产生16路时隙的电路。

上图中当frame来到时,计数器被清零,开始新的一帧。

16-sx_t根据选择信号s和计数器信号q[8..4]来产生16个时隙,程序如下:

SUB DESIGN 16_sx_t

(q[8..4],S = INPUT;

fS [ 15 . . 0 ] = OUTPUT ; )

BEGIN

IF s= = 0 THEN

FOR i IN 0 t0 15 GENERATE

fS li I = (q 18 . . 41 = = i ) ;

END GENERATE ;

ELSE FOR i IN 0 to 15 GENERATE

fs lil = (q[8 . .4] = = i+ 16) ;

BND GENERATE ;

END IF;

END;