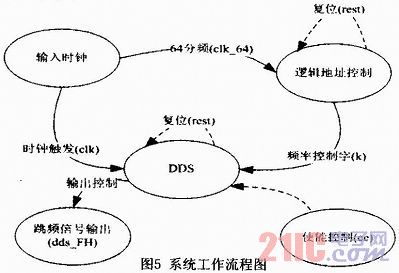

如图5所示,系统时钟clk经过64分频得到clk_64。逻辑控制单元由6级移位寄存器构成。在每个clk_64上升沿到来时,逻辑控制单元将产生一个6位的频率控制字(k)。当DDS使能信号ce为高电平时,DDS将停止工作。当ce为低电平时,在clk上升沿时DDS被触发,在当前状态下k的控制下,得到相应地址所对应的信号幅值。当k没有变化时,DDS输出正弦信号的频率没有任何变化,在一个clk_64上升沿到来时,k发生变化,从而使得DDS输出的正弦信号的频率发生变化。当复位信号reset为高电平时,逻辑地址控制单元和DDS单元同时回到初始状态,并保持不变,输出端dds_FH输出一直为零。当reset变为低电平时,在一个clk上升沿时系统开始工作。

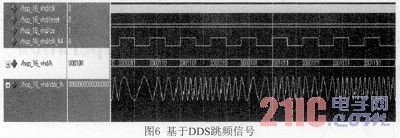

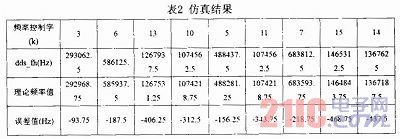

为方便观察仿真结果,本设计采用ModelSim SE 6.1d作为仿真波形测试软件。通过3.1节分析,由于本设计的DDS所产生的频率性能稳定,且跳频信号的误差并不累加。因此本节只给出仿真结果,不做其性能分析。图6为基于DDS的跳频信号,图6给出图5中各个控制信号的仿真结果。表2中给出图6中不同频率控制字所对应的正弦信号的频率与理论值的对比,可以看出本设计的DDS与理论值的误差较小。由于ROM中存储的点数较少,更加节省资源。

4 结束语

在FPGA硬件平台下设计基于DDS的跳频信号产生系统,不仅实现了大量数据快速运算,提高了仿真的速度,而且可以灵活、重复地对系统的参数进行优化配置,便于提高跳频系统的性能。本文所设计的DDS,结构简单、硬件资源占用率少,且产生频率相对准确。根据对所需跳频信号精确度要求的不同,合理配置参数,协调硬件资源与频率准确之间的矛盾关系,最终实现跳频系统的最优配置。