摘要:介绍了一种频率合成技术的设计与实现,基于DDS与PLL的技术产生高频信号频率。该频率合成器由高性能DDS芯片AD9852与锁相环芯片ADF4360-7构成。该方案控制简单、编程灵活、可靠性高,且产生的信号具有输出频率高、分辨率高、频谱纯等优点。

关键词:DDS;锁相环;FPGA

0 引言

频率合成技术是近代电子系统和装备的重要组成部分,在无线电技术和电子系统的各个领域均得到了广泛的应用。频率合成即把若干个稳定的标准频率经过“加、减、乘、除”四则运算,产生一系列新的具有同样稳定度和准确度的频率的过程。目前的频率合成的基本方法包括:直接频率合成(DS)、间接频率合成(IS)以及直接数字频率合成技术(DDS)。直接数字频率合成是将数字处理的技术与方法引入信号合成领域的一项新技术,它从相位的概念出发进行频率合成,通过DSP或FPCA对DDS输出波形的频率、幅度、相位实行精确的控制。本文采用DDS与PLL相结合的方式,并在FPGA的控制下,产生高频率、高分辨率以及短频率转换时间的信号波形。

1 方案拟定

1.1 DDS基本原理

典型的DDS由四部分构成,分别为:N位相位累加器、波形存储器、数/模转换器和低通滤波器。其原理为:由一个高稳定的晶体振荡器提供参考时钟频率,用于DDS中各部分同步工作。将频率控制字K送入相位累加器的输入端,相位累加器在参考时钟的作用下,按照频率控制字K对频率进行线性相位取样;对波形存储器寻址,使相位码转换为相应的波形幅度码;再经过数模转换器得到模拟的阶梯波;最后经低通滤波器得到所需频率的波形。

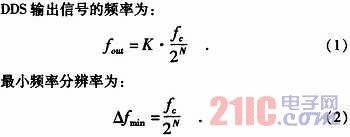

设fc为参考时钟频率,频率控制字为K,N是相位累加器的字长,则

1.2 DDS+PLL技术的优势

DDS具有极高的频率分辨率、近似实时的频率转换时间、任意波形的输出和便于程控等特点,但其合成频率较低,则限制了它的应用范围。而PLL具有的频带宽、工作频率高、频谱纯等优点正好可以弥补DDS的不足之处。两者的结合,不仅简化了电路、减少了硬件的使用量,同时还降低了功耗。

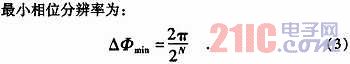

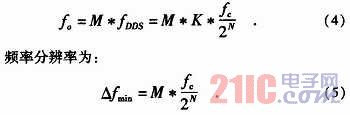

DDS的输出信号作为PLL的参考频率源,使得输出具有较高的频率分辨率,同时PLL作为一个可编程的倍频器,可将DDS产生的频率倍频到所需要的频率范围。当锁相环锁定的时候,频率合成器的输出频率为:

其中fc为DDS的时钟频率,K为DDS的频率控制字,N为DDS的相位累加器字长。

通过(5)式可知,基于DDS与PLL技术的频率合成器中,DDS可以输出一个低频信号,通过PLL的倍频合成后达到高频信号的输出范围,与此同时系统输出的信号也能有较高的频率分辨率。

2 频率合成器实现

2.1 方案设计

本设计采用DDS激励PLL的方式实现频率从低频倍频至高频。其中,DDS芯片选取AD公司生产的AD9852,PLL芯片选取AD公司生产的ADF43 60-7芯片。外部通过FPGA对DDS实现控制工作,其无限次反复编程的功能保证了DDS波形产生的持续时间大于锁相环的捕捉时间,从而产生

所需的输出频率。

AD9852的DDS系统有双48 bit可编程频率寄存器,在数据进入正弦查表之前截断,只对高17位进行正弦查表,最后再由内部集成的12 bit DAC产生模拟信号输出。它的内核部分最高可以工作在300 MHz,时钟信号可直接或者间接通过可编程时钟乘法器(4×—20×)输入内核,通过间接的方式降低外部时钟的频率,而内核的时钟频率保持不变。本设计基于间接时钟输入的方式,以30 MHz外部有源晶体振荡器提供稳定的时钟频率输入,通过内部可编程时钟乘法器进行4倍频,保证了工作频率为120 MHz。

锁相环输出部分采用的是ADF4360-7芯片,其输出频率从350 MH~1 800 MHz,且内部集成VCO,可由外部电感值的改变选择不同的工作频段。主要由低噪声数字鉴相器、可编程分频器R(14 bit)、可编程A(5 bit)、B(13 bit)寄存器和一个双模分频器(P/P+1分别为8/9,16/17)构成。其合成的分频比满足:N=B×P+A,其中,B≥A且N≥(P2-P)。