(1)空闲模式

在空闲模式下,即读操作和写操作都不工作的情况下,当O存在Q点时,M3打开,Qbar保持在VDD,同时M2,M4是关闭的,此时Q点的数据0可能受到漏电流IDS-M2漏电堆积,从而在Q点产生一定电压,甚至可能导致Q点数据翻转,产生错误逻辑。因此要利用M1管的漏电流,主要是M1的亚阈值电流,为了这个目的,需要在空闲模式下将位线

拉到地,同时将字线WL保持在亚阈值工作的条件下,这样就可以无需刷新正确存储数据0。当1存在Q点时,M4,M2打开,在Q和Qbar之间有正反馈,因此Q点被M2管拉到VDD,Qbar被M4管拉到地,但是此时M1管是处在亚阈值条件下,因此有一条路径从VDD到

,这会导致Q点数据不稳定,甚至有可能翻转,由于流经M2的电流远远大于流经M1的电流,数据相对还是比较稳定的。另一条位线BL拉到地,在空闲模式下读路径这端漏电流很小,可以忽略。

(2)写循环

写1操作开始,WL高电平打开M1管,读控制管RL关闭,

充电使得

=1,BL=0,Q点开始充电到1(此时由于NMOS管传递的是弱1),从而打开M4管,使Qbar=0,同时正反馈打开M2管,将Q点保持在强1;相反,写0操作的时候,位线

放电到

=0,打开字线WL,Q=0,同时打开M3管,Qbar=1。在结束写操作后,单元进入空闲模式。

(3)读循环

读操作主要由M5,M6管负责,Qbar连接到M5管的栅极,BL充电到高电平。读1的时候,Q=1,Qbar=0,M5关闭的,因而灵敏放大器从BL读出的是1;当读0操作的时候,WL字线关闭的,RL开启,Q=0,Qbar=1,管子M5开启,M5管和M6管共同下拉BL,读出数据0。在结束读操作后,单元进入空闲模式。

2.1 噪声容限

噪声容限是在没有引起单元翻转前提下引入存储节点的最大噪声电压值。在读操作的时候,噪声容限对于单元的稳定性更加重要,因为在传统的SRAM中读噪声容限和读的电流是冲突的,提高读电流速度的同时会降低读噪声容限为代价,所以在传统SRAM结构中,读电流和读噪声容限不可以分开独立调节,两者是相互影响制约的。而新结构采用独立的读电流路径,不包括存储节点,因而在读操作的时候,位线上的电压波动和外部噪声几乎不会对存储节点造成影响,从而大大的增加了读噪声容限。

2.2 漏电流

从以上分析可知,当数据存0的时候,新型6T-SRAM是通过M1管的亚阈值电流来保持数据的;当数据存1的时候,由于M2,M4的正反馈作用,并且在空闲状态下M1处于亚阈值导通状态,所以存在从电源电压到地的通路,这些都会导致漏电流的增加图3显示了这条路径。在大部分数据和指令缓存器中,所存的值为0居多,分别占到75%和64%。基于这些考虑,在标准0.18μm CMOS工艺下,对普通6T-SRAM和新型6T-SRAM进行了平均漏电流仿真。传统6T-SRAM漏电流为164 nA,新型6T-SRAM漏电流为179 nA,新型SRAM比传统的大9%,这是可以接受的范围因为新型SRAM采用漏电流保持技术,从而不需要数据的刷新来维持数据,另外漏电泄露不会在Q点产生过高的浮空电压,因而数据更加稳定。

2.3 功耗

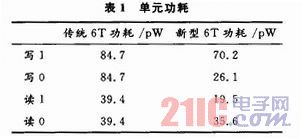

一般而言,位线是产生动态功耗的主要部分,所以说往往在读/写操作转换过程中位线的变化会消耗主要的功耗,本文对传统6T-SRAM和新型6T-SRAM单元结构进行了功耗仿真,如表1所示。

表1中可以看出,在传统的6T-sRAM读/写过程中,对称结构的两个位线电压的变化是一致的,因而功耗是相同的。新型6T-SRAM单元功耗比传统单元低了很多,这是因为在读/写操作的时候,参与工作的管子数量少,并且只有一个位线参与工作,并且在写0的时候,由于位线是0,所以功耗很低。

上一页 [1] [2] [3] 下一页