3.4 Avalon Master 模块

Avalon_Master 模块设计一个状态机控制电路,完成在Avalon 总线上的地址、Byteenable、读写控制信号、读数据信号和写数据信号的产生与控制处理。同时还有等待读数据到来以及读数据确认工作。

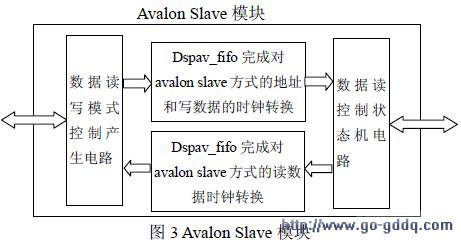

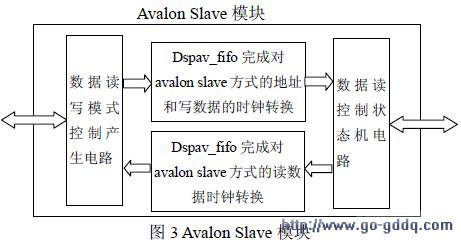

3.5 Avalon Slave 模块

Avalon_Slave 模块是一个Avalon 总线的从设备,它可接收Avalon 总线上其它主设备发送过来的数据写请求、数据读请求,同时将从通过Host 接口读到的数据按相应的总线规则送到数据总线上,同时产生数据有效信号。由于这里的设计采用可变读等待设计,同时还需要完成对TS101 数据读取换钟转换。该模块主要由以下三部分构成:

1. ts101_slave_address_fifo 模块模块完成在Avalon 总线上的主设备控制系统总线时,Avalon 总线到DSP 总线的地址及写入数据的换时钟控制。

2. ts101_slave_readdata_fifo 模块模块完成在Avalon 总线上的主设备控制系统总线时,DSP 总线到Avalon 总线的读入数据的换时钟控制。

3. 数据读控制电路部分完成读数据的确认以及读值有效信号的产生。

3.6 Host Slave 模块

Host_Slave 模块为一个控制状态机电路,它根据Avalon_Slave 模块提供的信号完成对DSP 的主总线控制请求,带发送信号的组织,发送和接收信号的确认接收,包括产生HBRN信号,并根据HBGN 信号的状态产生读写控制信号、读写地址信号、写数据信号以及从DSP中读回待接收的读数据信号。

4. 功能测试

目前,ALTEra 的RapidIO IP 核支持的RapidIO 事务有:读操作NREAD 请求和响应,写操作NWRITE 请求,带响应的写操作NWRITE_R 请求和响应,流写(SWRITE)请求,维护(MAINTENANCE)读请求和相应,维护(MAINTENANCE)写请求和响应,维护(MAINTENANCE)端口写请求,门铃(DOORBELL)请求和相应。在实际的测试中,将这个电路板和Mercury 公司Ensemble MPQ-101 同时安装在SILIContkx 的串行RapidIO 开发平台上,结果证实DSP 通过转接桥逻辑控制RapidIO IP 核,已经实现了所有的这些事务。

5. 总结和展望

RapidIO 作为下一代嵌入式互联技术,在国内的信号处理平台上的运用越来越广泛。但是目前很多处理芯片不具有RapidIO 的接口。利用FPGA可以方便快速定制一个合适的接口,为RapidIO 网络增添各种丰富的节点。同时,本文给出了实现这个转接桥的思路做了详细讨论,这样不同的DSP,甚至CPU 都可以利用这种思路来接入RapidIO 网络。

在目前的设计中,一个 FPGA 为一个DSP 提供转接桥逻辑,过于浪费FPGA 的资源。在紧接下来的设计中,我们将4 片DSP 组成一簇接入FPGA,从而提高单板的处理能力,同时提高了FPGA 的利用率。(

上一页 [1] [2] [3] 下一页