什么是FPGA?

在密集型实时信号处理应用中,DSP 由于其本身结构特点具有不可替代的位置。但是遗憾的是目前很多DSP不具有RapidIO 接口,而且也没有ASIC 能够为这些DSP提供RapidIO接口。为了在RapidIO 网络中充分利用DSP 数据处理的优势,我们采用FPGA 做一个转接桥逻辑,将DSP 的总线连接到一个RapidIO 的IP 核,从而实现DSP 和RapidIO 网络的互联。

1. 总线结构概述

1.1 总线结构的演化

高速通信和超快速计算的需求日益增大,使得多处理器以及各种外部设备协同工作才能满足实时快速的要求。传统的系统中,这些处理器、处理器簇、外设之间的数据交互是基于并行的共享总线方式进行。从单分段总线到级联的多分段总线,这些基于共享总线的体系结构中,所有的设备通讯竞争带宽,这样交互数据成为了整体系统性能的瓶颈。不仅如此,并行总线所需要的大量IO 引脚也给系统的电器性能和机械性能带来相当的考验。因此,提高系统性能就迫切需要一种新的体系结构。

目前新型的体系结构是基于点对点串行交换结构的体系。相比传统的并行共享总线结构,串行交换结构中的两个端点交互数据不影响其他端点之间的数据交互,从而大大提高了系统带宽,除此之外,串行交换结构所需要的引脚也大大减少了,而且串行结构采用的差分线连接也提高了信号传输的距离和可靠性。当前流行的串行交换结构主要有PCI-Express,InfiniBand,RapidIO 等。这些总线结构的应用范围既有交叉有各有侧重。

1.2 RapidIO 交换结构

RapidIO 互连架构,它的设计与最流行的集成通信处理器、主机处理器以及网络数字信号处理器相兼容,是高性能包交换互连技术。它满足了高性能嵌入式系统行业对内部系统互连的需求,包括可靠性、高带宽和更快的总线速率。相比PCI、PCI-X、PCIE 和Infiniband来说,RapidIO 主要特性是具有极低的延迟性和高带宽,并很容易实现和PCI、PCI-X、PCIE、FPDP、以太网等的桥接,适合用于芯片与芯片、板与板、系统与系统之间的高速数据传输。

2. 系统设计

2.1 工程背景

多片 DSP 形成处理器簇,共同完成快速实时的运算已经成为现代信号处理机一种流行的方式。但是目前大多数DSP 都不具备RapidIO 接口,所以我们采用FPGA,将DSP 的总线与一个RapidIO IP 核总线相连接,实现DSP 与RapidIO 网络的通信。

2.2 芯片选型

我们选用 Analog 的TigerShark101(以下简称TS101) DSP, ADSP-TS101S 是TigerSHARC 处理器系列中的首款器件。FPGA 选用ALTEra 的Stratix II GX 60 芯片。

Altera 的RapidIO 的IP 核兼容于2005 年2 月发布的RapidIO 互连标准1.3,实现了3种标准速度1.25G、2.5G、3.125G 下1x/4x 的物理层协议。同时,Altera 公司的SOPC 工具提供了大量的成熟的IP 核和可裁剪的Avalon 总线,方便的帮助用户实现模块化设计。

2.3 系统结构

将 TS101 的总线桥接到FPGA 的Avalon 总线上。其中,DSP 芯片是用来做大量的数据处理,FPGA 是DSP 和RapidIO 之间通讯的桥梁。FPGA 内的RapidIO 接口有成熟的IP 核,将DSP 和RapidIO 的IP 核连接的关键在于实现DSP 外部总线到IP 核Avalon 总线的转换。

TS101 内部有一个寄存器SYSCON,用来控制外部端口、主机接口、多处理器接口的数据位宽、插入的等待周期、流水线深度等设置。由于这个寄存器在上电后只能修改一次,这里我们将外部端口配置位32 位的慢速协议,完成RapidIO 的维护,门铃等事务;将主机接口配置位64 位的流水线协议,完成高速的IO 事务。通过转接桥逻辑的转换。

3. 转接桥设计

3.1 转接桥总体结构

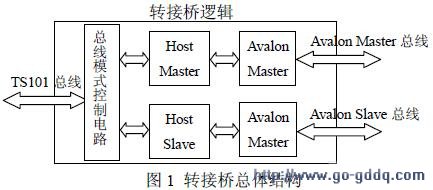

转接桥逻辑为 TS101 总线接口与Avalon 总线接口转换器,由四个模块及辅助电路构成。

3.2 总线模式控制电路

总线模式控制电路完成根据系统请求情况切换 TS101 总线端地址、数据以及相应的控制信号的输入输出方向、功能及状态。其中需要控制的部分包括:数据总线的输入输出方向连接及模式控制,地址总线的输入输出方向连接及模式控制,TS101 的读控制信号的输入输出方向连接及模式控制,TS101 的写控制信号的输入输出方向连接及模式控制,TS101 的ACK 信号的输入输出方向连接及模式控制。另外,该模块中还完成一些控制信号的连接。

3.3 Host Master 模块

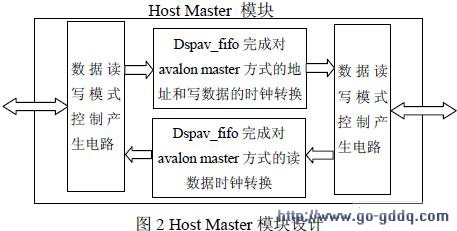

Host_Master 模块完成在系统工作于TS101 侧控制模式时对Avalon 总线进行读写的总线时钟切换和相关部分工作时的控制。它大致可分为四部分完成:

1. 数据读写控制产生电路在数据写时根据输入管脚中的片选信号、写信号,将DSP 要写入Avalon 总线的地址及数据写入host_address_fifo 中。当是数据读时,根据输入管脚中的片选信号、读信号,将DSP 要写入Avalon 总线的地址写入host_addrfifo 中,同时产生数据读等待信号,当从host_readdata_fifo 总线读到数据后,该电路撤销读等待信号,并将得到的数据送入TS101 的数据总线。

2. host_address_fifo 模块完成在TS101 控制系统总线时,DSP 接口时钟到Avalon 总线地址及写入数据的换时钟控制。

3. host_readdata_fifo 模块完成在TS101 控制系统总线时,Avalon 总线到DSP 接口总线的读入数据的换时钟控制。

4. 数据读控制状态机电路部分完成TS101 的读控制信号的产生,以及读到的数据信号的存储控制。

(