2.3 plane模块设计

2.3.1 简化 plane预测模式

Intra_16×16_Plane模式和色度块Intra_chroma_Plane模式是帧内预测中最复杂的预算模式,为了满足系统实时处理的要求,可提前预算plane模式需要的一些参数。本文以Intra_16×16_Plane为例介绍如何简化plane模式,Intra_chroma_Plane方法类同。

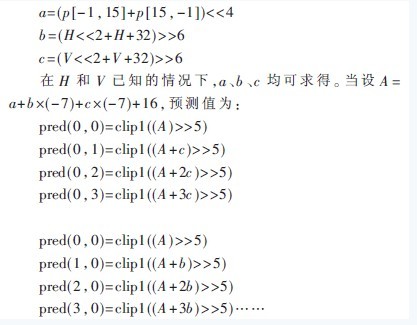

在plane模式运算中要用到乘法,为了节约硬件资源,采用移位来实现乘法,其中参数a、b、c的计算公式为:

上述公式,首先求得A后,pred(0,1)、pred(0,2)、pred(0,3)的值是在A的基础上加上c、2c、3c,然后再进行移位和clip。pred(1,0)、pred(2,0)、pred(3,0)的值只是在A的基础上加上b、2b、3b,然后再进行移位和clip。所以提前求得A、b、c,预算值是在A的基础上加上b或者c的倍数,本方法可大大优化plane模式。

2.3.2 plane模式硬件设计

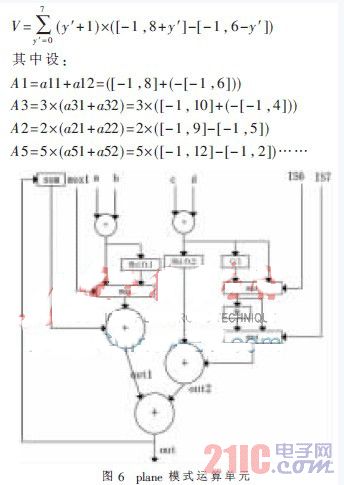

plane模式的关键是求得参数H和V,其硬件设计如图6所示。以V为例介绍本电路。

举例说明本运算单元如何计算出参数H:

当a=a11、b=a12、c=a3、d=a3、sum=0、mux1=0、IS6=0、IS7=0、shift1=0、shift2=1时,就可以求得A1+A3。a=a21、b=a22、c=a51、d=a52、sum=0、mux1=0、IS6=0、IS7=0、shift1=1、shift2=2时,就可以求得A2+A5,并依照这个运算单元可求出A4+A6和A8+A7。

本电路4个时钟周期就可以求得H或V,所以共需要8个时钟周期求H和V。本方法与通常方法相比,只计算一次A、b、c的值,其他位置的预测值只需要在A的基础上加上b或者c的倍数,降低了复杂度。

3 实验结果

本设计使用Verilog HDL完成硬件代码的编写,并用ALTEra公司的QUARTus II 8.0进行代码的仿真和综合。图7为核心单元preDICtion模块的仿真结果,PE0_out、PE1_out、PE2_out、PE3_out9为4个并行单元的输出。采用Altera公司的Cyclone II进行本设计FPGA验证,本设计占用的逻辑资源数量较少,节约了硬件资源。

本文根据H.264帧内预测的特点,提出了一种并行处理的硬件实现方法。该方法能够提高帧内预测的处理速度,节约了硬件资源,满足了高清视频的解码要求。