����һ������

����������Ź�˾�����й�ע��������������3G��Ʒ�����ƺͿ����������ƶ��նˡ���վ�Լ����������������豸�������ɵأ�3G��Ʒ��ҵ���Ѿ���Ϊ����ͨ���г���������������CDMA�������ǿ���CDMA(W-CDMA)ƾ����������ܡ���ϵͳ���������еĸ�Ч���Լ�������Դʹ���еı���ԣ������Ϊ3G�����е�������

����Ϊ������3G�ĸ������Ӷ��Լ����źŴ���Ҫ����FPGA/ASIC��ר��Ӳ������Ҫ���ϲ�ͬ�û���Ʒ�Ĺ��Ҳ����˵����3G�����ն˷�չ�У���Ʒ�ijߴ硢�����Լ�����������Щ��������ʮ�ֹؼ�����Ҫ�ľ������ء��ɴˣ�ϵͳоƬ(SoC)��Ϊһ���µ���Ʒ��Ա�������3G�ķ�չ��SoCҪ���ܹ���������Ч�źŴ����㷨��ṹ����ơ���չ��������һ��С��оƬ�ϡ�

���������˲�����Ϊ�źŴ�������Ϊ������Ԫ�������㷺��Ӧ��������ͨ�ŵĸ��������С��������3G��CDMA 2000�е��������FIR�˲�����ASICʵ�ֽ������ۣ����ڴ����һ��ʵЧ��ʵ�ֽṹ�����ڷֲ�ʽ����(DA)�ṹ�IJ������������������˲�����������˲���������ּ������ź�Ƶ�״���Ч�ʵĻ���ͨ�Ŵ����С�����D/Aת����ij����˲���ͨ���DZ����ΪFIR�˲������������ǣ�1�ݣ����źŵ�ͬ��(I)������(Q)����ת��Ϊģ���I��Q�źš�

����һ����˵��FIR�˲�������Ҫ��һ�������һ�����ƽ���������ҳ���������Ӧ�ġ�������Ҫע����ǣ������˲����IJ�������һ��Ҫ��������I��Q��������Ҫ��(ͨ������4~8��)����ˣ��ڴ�Ҫ��һ������������εĹ�������ͼ1�����˵��͵ij��ι��̣����й�����ͨ�����������������ֵ�в���M-1����ֵ��ʵ�ֵġ�CDMA2000���У���1����Ƶ���ʵ�ϵͳ(��Ƭ���ʣ�1.2288 MCPS)����48�Գ�ϵ��FIR�˲�������3����Ƶ���ʵ�ϵͳ(��Ƭ���ʣ�3×1.2288 MCPS)����108���˲����������˲���������4����Ƭ�����£���������I��Q����Ӧ���ǹ�������4������ͼ1��M��4��

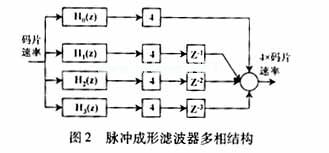

����FIR�˲������ݺ���ΪH(z)������ʮ����/�岹���ۣ�2�ݣ�ͨ����ͼ2��ʾ��H(z)�Ķ���ֽ�(��ͼ����M��4)���ܸ���Ч����ɹ��������˲������ܡ���ͼ2�У�Hk(z)��ʾ���˲����Ĵ��ݺ�������������Ӧhk(n)=h(4n+k), n=0,1,…11���ɶ�h(n)��ֵ�ó��ġ�����ṹ���ŵ����ڣ��������˲����ǹ����ڽϵ͵ij��������ϵģ�����4�����˲������Ϻ���ϵ����ֵ��ԭ���˲�����H(z)ϵ���൱��Ҳ����˵�������������������ļ��������ܼ���3/4��ͬʱ��ͼ2���Կ��������ַ�����Ҫ�õ�4���˲�������˾�Ӳ������Ч����˵���Ⲣ����������ġ�

���潫����һ�ֽṹ������ASIC��˵�����ӵ�ʵ�ʡ�ʵЧ��ͬʱҲ�����˶���ֽ���ŵ㡣

�����ֲ�ʽ������ϵ

�ڷֲ�ʽ����(DA)���㷨���У��˲�����������Ա�ʾΪ

![]()

����ak�ǹ̶����˲���ϵ��;��

xk�����������֡���

�����xk��ʾ��B���صĶ����Ʋ��룬|xk|<1������

![]()

����bkiȡֵΪ0����1,bk0�Ƿ���λ,bk0Ϊ1��ʾ����Ϊ����bk0Ϊ0��ʾ����Ϊ����bk,B-1�������Чλ(LSB)����(2)ʽ��(1)ʽ�ϲ������ǿ��Եõ�y����ı���λ����ʽ��3�ݣ�

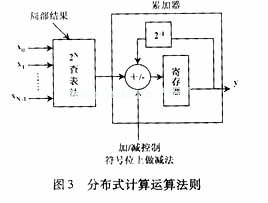

����bkiȡֵֻ��0��1�� ��(4)ʽ��ֵ��2��N�ֿ����ԡ���ˣ�����Ԥ�������2N���ֲ�����������һ���̶��ı���(���Ŀ���Ϊ��ϵ��ak����Ŀ��ȣ����Ϊ2N)��N���ܹ�������Դ�������ݽ��д��������ݳ��ȣ�3�ݡ�Ȼ������������ݣ�ֱ�ӶԸñ�Ѱַ������������ۼ����С���B-1�β��֮���ۼ����ļĴ����洢��(3)ʽ��һ����ʾ�Ľ�������һ����������ֲ���� ��Ҳ����(3)ʽ�еĵڶ�����ڱ�ʾ����λ�������ڼĴ���������λ�����в���������������ӼĴ��������ƹ����м�ȥ����ˣ�������������ֻ���ڷ���λʱ���ϻ�ʹ�ü������ơ���

��Ҳ����(3)ʽ�еĵڶ�����ڱ�ʾ����λ�������ڼĴ���������λ�����в���������������ӼĴ��������ƹ����м�ȥ����ˣ�������������ֻ���ڷ���λʱ���ϻ�ʹ�ü������ơ���

DA���㷨����ͼ3��ʾ������Ļ��������У�������ӷ��������Լ������������е���λ������DA�ṹ��ǰ���ǣ��������ֵ����Ҫ��ʾΪ2�����벢����ת����һ�����ش�����ʽ���ܹ���Ҫ��N��B���ص���λ�Ĵ�����ÿ���Ĵ�����һ��ʱ�������²���1����������һ�����ڲ��ұ���LUT����ַ(N���ؿ�)��LUT�洢�������˲���ϵ��״̬���ܵľֲ��������Щ�ֲ�����ڼĴ����н��м�Ȩ(ÿ�����ڳ���2)���ۼӣ�ֱ��ÿ����λ�Ĵ��������һλΪֹ��

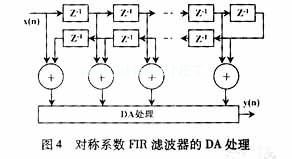

������������˲������ŶԳƵij����Ӧ������Ȱ�ʹ��ͬһ��������Ӧϵ����2������ȡ��ֵ������ӣ�Ȼ����̵ذ�N/2���ӷ���������������DA���д���,��ͼ4��4����ʾ�����ԣ�LUT�ĸ���Ҳ�ʹ�2N�����ٵ���2N/2����