2.5 电平转换的电路设计

由于CPLD输出的驱动脉冲电压为3.3 V,而CCD工作所需的驱动脉冲为5 V,所以需要在CPLD和CCD之间加入—个电平转换电路。电路原理如图6所示。

3 软件设计

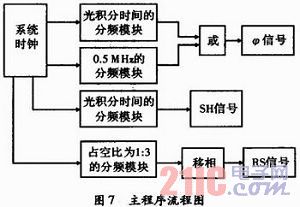

系统软件采用Verilog HDL硬件描述语言,按照模块化的思路设计,将要完成的任务分成为多个模块,每个模块由一个或多个子函数完成。这样能使设计思路清晰、移植性强,在调试软件时容易发现和改正错误,降低了软件调试的难度。程序中尽量减少子函数之间的相互嵌套调用,这样可以减少任务之间的等待时间,提高系统处理任务的能力。主程序如图7所示。

SH是一个光积分信号,SH信号的相邻两个脉冲之间的时间间隔代表了积分时间的长短。光积分时间为5 416个RS周期,对系统时钟进行光积分的分频,实现了SH信号脉冲。在光积分阶段,SH为低电平,它使存储栅和模拟移位寄存器隔离,不会发生电荷转移。时钟脉冲φ为典型值0.5 MHz时,占空比为50%,占空比是指高电平在一个周期内所占的时间比率。它是SH信号和占空比为50%的一个0.5MHz的脉冲信号叠加,所以0.5 MHz的信号和SH信号通过一个或门,就可以实现φ信号;输出复位脉冲RS为1 MHz,占空比1:3。此外,RS信号和SH、φ信号有一定的相位关系,通过一个移位寄存器移相,来实现RS脉冲信号。

4 仿真实验

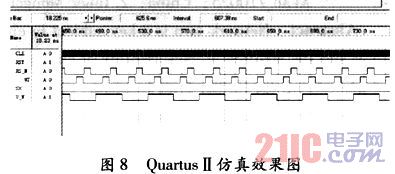

系统时钟周期部分设置为1 ns,正常工作时复位信号RS为高电平,然后对RS、φ、SH信号进行仿真,结果如图8所示。

5 结束语

研究的线阵CCD驱动电路主要是以CPLD为驱动中心而设计,这种方案减少了以往驱动电路的电路体积大、设计复杂、调试困难等缺点,增加了系统的稳定性、可靠性,集成度高且抗干扰能力强。通过对硬件和软件大量的模拟实验表明,文中所研究的线阵CCD驱动脉冲信号能够满足CCD工作所需的基本功能,达到了设计要求。