摘要:针对目前嵌入式存储器测试算法的测试效率与故障覆盖率难以兼得的现状,提出了兼顾二者的测试算法。实验结果表明该算法最适合对存储器进行大批量的测试。在测试效率上的优势很明显,故障覆盖率也能达到应用标准。

关键词:存储器测试;嵌入式存储器;故障覆盖率;外围互连线

引言

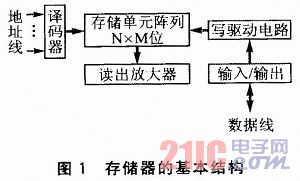

随着微电子产业日新月异的发展,IC设计的规模与集成度越来越大。SoC是现阶段IC设计的标准结构之一,通常由CPU核、存储器、逻辑电路、各种外设及接口组成,而存储器通常占据芯片的绝大部分。常用的嵌入式存储器有ROM、Flash、SRAM、DRAM等。典型的存储器的基本结构如图1所示,存储器主要由地址线、数据线、控制线、地址译码器、存储单元阵列、输入/输出电路、读出放大器、写驱动电路等部分组成。

嵌入式存储器的测试主要分为3类:

①直流参数测试(DC Parameter Testing)——校验工作电流、电平、功率、扇出能力、漏电流等参数特性。

②交流参数测试(AC Parameter Testing)——检测建立时间、保持时间、访问时间等时间参数特性。

③功能测试(Functional Testing)——测试存储器件的逻辑功能是否正常,对存储单元、读出放大器、写驱动等产生的物理故障进行检测。

本文主要讨论第3类中嵌入式存储器的功能测试。

1 采用的方法

现有的嵌入式存储器测试算法都是直接对存储器内部单元直接测试,所用的算法在测试复杂度和故障覆盖率之问难以找到一个平衡点。本文介绍的方法采用外围互连线测试和内部单元结合的测试算法,摒弃了以往只是测试内部单元的算法,提高了测试效率,故障覆盖率也有所提升。

外围互连线测试:假设存储器本身功能正常,控制线也总是可控的,故障只是由于器件装配引起的,需要对存储器的地址线和数据线可能的短路和开路故障进行测试。

内部单元测试:对存储器的译码、读写等功能进行测试。

两种测试的目的不一样。内部单元测试的目的在于判断内存单元的好坏,所以在程序设计中只要发现故障就可以终止退出,同时报告发生故障的内存单元;外围互连测试的目的不仅仅在于发现故障,而且还要求能对故障进行精确定位。所以在算法设计中需要将这两步测试过程按顺序执行完毕。

2 嵌入式存储器测试的故障模型

对故障机理进行分析,建立相应的故障模型是产生算法的前提。

2.1 外围互连线测试的故障模型

对于外围互连线,本文采用的是固定故障模型,固定故障也是存储器外嗣互连线的主要故障。固定故障模型包括固定逻辑故障、固定开路故障和桥接短路故障。固定逻辑故障是指由于物理缺陷,数据线或者地址线的状态不受输入的控制,绑定到逻辑O或者1状态,包括S-A-1(Stuck-at-1)和S-A-0(stuck-at-0)故障。而在外围互连线测试中,固定开路故障和桥接短路故障往往可以等价于S-A-0或S-A-1的固定逻辑故障,在此不作赘述。