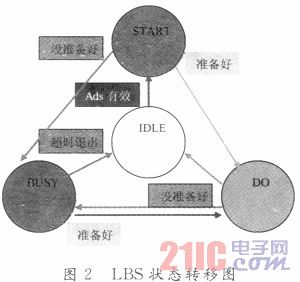

IDLE:空闲状态。

START:当ADS地址选通有效时进入此状态,进行地址空间判断。

DO:当地址空间有效,并且传输条件满足时进入传输状态,每个时钟判断条件,当条件满足时继续该状态,当条件不满足时,进入BUSY等待状态,传输结束(BLAST有效)进入IDLE状态。

BUSY:当数据没准备好时,在BUSY状态等待,当数据准备好后进入DO状态,当超时后进入IDLE状态,实时退出。

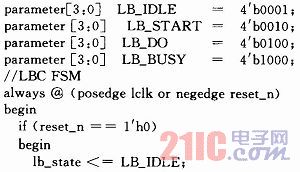

2.5 LBS状态机工作流程

FPGA作为LBS的逻辑控制器,负责协调好与DDR_FIFO数据和PEX8311之间的时序关系。系统接收数据时,首先由驱动程序向PEX8311发送复位信号,通过LRESET复位LBS本地端的FPGA,清空FPGA内部DDR_FIFO内部数据,并将HF和FF标志置为无效,然后等待数据的输入。FPGA读入DDR数据后,首先将DDR数据写入DDR_FIFO中,当DDR_FIFO中的数据达到半满状态时,HF标志位有效,通过FPGA向PEX8311发出DMA中断请求。PC机响应中断后,设置DMA传输模式,传输字节数及地址信号等。PEX8311通过LHOLD申请控制本地总线,此时FPGA发出的LHOLDA响应信号后获得本地总线的控制权,并立即进入连续字节突发模式的BLOCk DMA周期即由IDLE状态到START状态。FPGA在收到有效的LW/R读信号和ADS地址选通信号后,进入DO状态,同时发出Ready本地准备好应答信号,使能DDR_FIFO的读允许REN和输出允许OE。在传输最后一个数据时,PEX8311发出BLAST信号,FPGA配置DDR_FIFO读使能和输出使能无效,并取消Ready从而结束DMA周期。PC系统发送数据时,FPGA将计算机通过PCIe传过来的LBS数据写入PC_FIFO中,再输出写入到DDR中。

2.6 LBS状态机核心编码设计

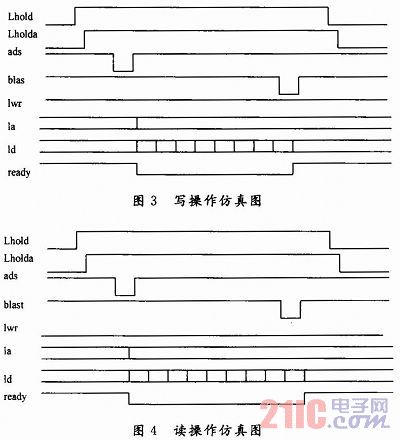

按照上述4个状态进行Verilog设计,经过仿真和上板调试,效果很好,下面是状态机设计程序,仿真时序图如图3,图4所示。