该方法省去了PT2272解码芯片,但仍然没有解决软件编程复杂,响应速度较慢的缺点。

1.3 PT2262/PT2272硬件编码译码实现多路控制法

PT2262/PT2272最多有6个数据端管脚(D0~D5)。因此,可以在不改变地址码的前提下,通过编码器对PT2262进行数据端管脚进行扩展,PT2272输出端管脚通过译码器解码,即可实现控制通道的扩展。例如,PT2262的6个数据端接2片8-3编码器,PT2272的6个数据端接2片3-8译码器,即可将6个数据端扩展成16个数据端。这里,我们可以用64-6编码器和6-64译码器最多可实现64(25)路控制通道,完全能满足一般控制的需求。同时,该方法省去了复杂的软件编程,保持了原有的硬件相应速度快的特点。

2 编码器和译码器对PT2262/PT2272的硬件控制

2.1 编码器和译码器的设计

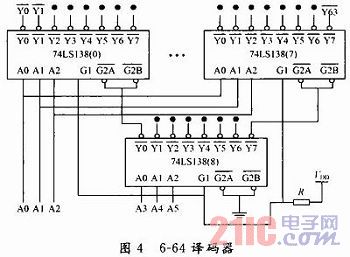

由于目前还没有64-6路编码器和6-64路译码器芯片,因此,需要用74LS148和74LS138通过级联方式实现。

9片74LS148和9片74LS138级联方式可以分别组成64-6路编码器和6-64路译码器,如图3,图4所示。

图3中,74LS148为优先编码器,EI为选通输入信号,EO为选通输出信号,GS为扩展信号。可以将8片编码器的EI信号和EO信号级联,优先级最高的编码器EI接地,则每次编码,只有一片编码器进行编码且GS输出低电平,其他没有进行编码的编码器输出均为高电平。因此,可以将8片编码器的输出信号分别通过CC4068芯片8输入与门电路输出,作为AOA1A2信号。8片编码器的GS信号分别接入74LS148(8)的输入信号,则进行编码工作的编码器的GS信号通过74LS148(8)再次进行编码,其结果作为A3A4A5信号。例如:输入163=0,则74LS148(7)工作输出A2A1A0= 000,GS=0,则A2A1A0=000;74LS148(8)的输入I7=0,由于EI=0,所以A5A4A3=000。即用9片74LS148实现了64-4的编码器设计。