1.3 阈值电压的设计

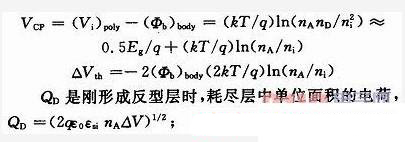

对于多晶硅栅的NMOS管,阈值电压可写作:

![]()

式中:Vcp是高浓度N+掺杂的多晶硅栅和P-body区的接触电势,△VTh是强反型下的表面势:

当达到和超出阈值电压时,△V=△Vth=(kT/q)ln(nA/ni);Qss是Si-SiO2界面杂质引入的电荷,通常它带负电。

1.4 导通电阻的设计

导通电阻Ron=Rcs+Rbs+Rch+Ra+Rj+Re+Rbd+Rcd。各部分的含义为:Rcs为源极引线与N+源区接触电阻,该电阻可通过适当的金属化工艺而使之忽略不计;Rbs源区串联电阻;Rch沟道电阻;Ra栅电极正下方N-区表面积累层电阻;RJ相邻两P阱间形成的J型管区电阻;Re高阻外延层的导通电阻;Rbd漏极N+层(即衬底)的导通电阻,由于此处杂质浓度较高,因此Rbd可忽略不计;Rcd为漏极接触电阻,其阻值较小,可忽略不计。

在200 V的器件中Rch起着主要作用:

![]()

理论上可以通过减小沟道长度或增加沟道内电子迁移率的办法来减小沟道电阻。但对于N沟道MOSFET器件,电子迁移率可近似看作常数,而沟道长度受到沟道穿通二次击穿的限制。目前通过增加沟道宽度即提高元胞密度是减小沟道电阻的主要方法。

1.5 参数的仿真结果

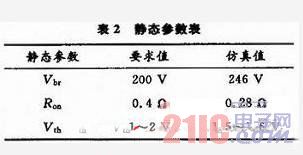

该器件用Tsuprem 4和MeDICi软件混合仿真。关键工艺参数为:外延厚度20μm,外延电阻率5Ω·cm;栅氧厚度52 nm(5+40+5 min);P阱注入剂量在3×1013cm-3,推阱时间为65 min。表2给出了静态参数表。

各参数仿真图如图1,图2所示。

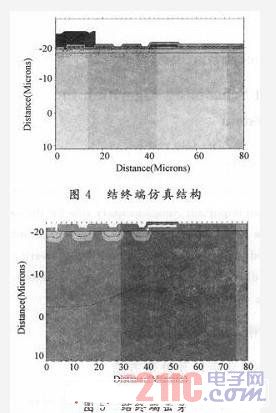

1.6 结终端仿真结果

结终端结合自对准工艺,P等位和场限环的形成依靠多晶和场氧进行阻挡,利用多晶硅作为金属场板。使用了1个等位环和3个场限环,耐压可以达到242 V,仿真结果如图3~5所示。

2 制造结果

在基于设计和封装控制的基础上,进行了样品的试制。采用的是TO-257的扁平封装。管芯试制样品后,对相关参数进行了测试,测试结果见表3所示。因为导通电阻是在封装之后测试,在封装后会引入一定的封装电阻,所以导通电阻比仿真时略有增大。随后对管芯进行了封装,试验产品出来后,发现有近一半产品的阈值电压有所缩小,有的甚至降到1V以下。出现这一问题,及时查找原因,发现烧结时间过长可能是阈值电压缩小的主要原因。由于本产品外形的特殊性,烧结时,每一船放的产品只数不能过多。而量少了,原来的烧结时间就显得过长。烧结时使用的是氢气保护,烧结时间长了,使氢离子在栅极上堆积,致使阈值电压下降。于是尝试着将烧结时间缩短,可是烧出来又出现了新的问题:很多产品的烧结焊料熔化不均匀,使芯片与底座烧结不牢,用探针一戳,就掉下来了。为了解决这一矛盾,反复试验将烧结时间用秒数来增减。最终达到在焊料完全均匀熔化的前提下,又使阈值电压不至于缩小。