功率MOS场效应晶体管是新一代电力电子开关器件,在微电子工艺基础上实现电力设备高功率大电流的要求。自从垂直导电双扩散VDMOS(VertICalDou-ble-diff used Metal Oxide SEMIconductor)新结构诞生以来,电力MOSFET得到了迅速发展。本文分别从管芯的静态参数设计方面,介绍了VMDOS(200 V)设计的方法以及仿真的结果,并对流片结果进行了比较。

1 芯片设计

1.1 芯片设计思路设计

高压的VDMOS器件,希望得到高的耐压容量,低的特征导通电阻。降低导通电阻的方法主要是:减薄外延厚度、降低外延层电阻率、增加栅长LG、降低P-body的结深(xp+wo);而高的耐压容量要求:增加外延层厚度、增加外延电阻率、减小橱长LG,P-body的结深对耐压的影响取决于P-body间距的减小和外延耗尽厚度的减薄哪个因素对耐压的影响更大。高压VDMOS的静态参数优化设计主要矛盾集中在外延的选择、栅长及P-body的结深的确定上。

1.2 VDMOS耐压的设计

使半导体器件耐压受到限制的电击穿有雪崩击穿与隧道击穿2种,隧道击穿主要发生在耐压小于7 V的低压器件中。在这里只讨论高压器件所涉及到的雪崩击穿。计算雪崩击穿的公式:

αeff=1.8×10-35E7cm-1

式中:E以V/cm为单位。

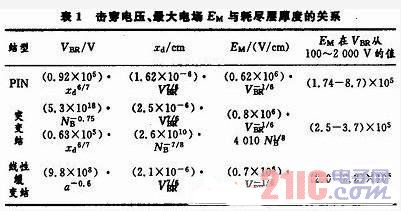

表1中列出了几种结的击穿电压、最大电场EM与耗尽层厚度的关系。

表1中:VBR的单位V,NB的单位为cm-3。NB对单边突变结代表轻掺杂区的杂质浓度,对双边突变结代表:

![]()

式中:NA及ND是两边的杂质浓度;a代表线性缓变结杂质浓度梯度单位为:cm-4。

当衬底杂质浓度NB低而a值大时,VBR过渡到最下方的斜线,与单边突变结一致;当NB高而a值小时,VBR与NB无关,这相当于线性缓变结的情形。

由于导通电阻随击穿电压猛烈增长,使得提高表面击穿电压在功率MOS中显得格外重要,因为若表面击穿电压低于体内很多,即等于此耐压的管子要以无谓增大导通电阻作牺牲来达到。为了提高表面击穿电压,功率MOS常用的终端技术有浮空场限环、场板等,有时还将这些技术结合起来使用,使表面击穿电压达到体内击穿电压的70 %~90%。

现代的终端技术已能使表面击穿电压达到体内理想一维电场分布的击穿电压的90%,在这种情况下,另一影响击穿电压的因素需要考虑,这就是每一个阱边角上的电场集中效应。当两个P阱之间距离很近时,边角电场出现峰值并不明显,击穿电压没有多大下降,但是P阱靠近则导通电阻也变大。由此可见,在这种情形下,高压器件的元胞图形对导通电阻又发生影响。计算表明方形阱最差,因为其角上为球面结,击穿最低。条状结构的P阱没有角,只有边,边上为圆柱结,击穿电压稍高,但条状结构有较高的导通电阻,仔细的研究结果表明,最优的结构是圆形元胞,而且两个P阱之间的距离应比由边缘电场决定的距离稍大。但是,圆形在制版过程和工艺对准方面有一定的困难,所以近似圆形的六角形成为最佳的选择。