・上一文章:基于CC2530的脉搏感知节点设计

・下一文章:详解有线电视技术

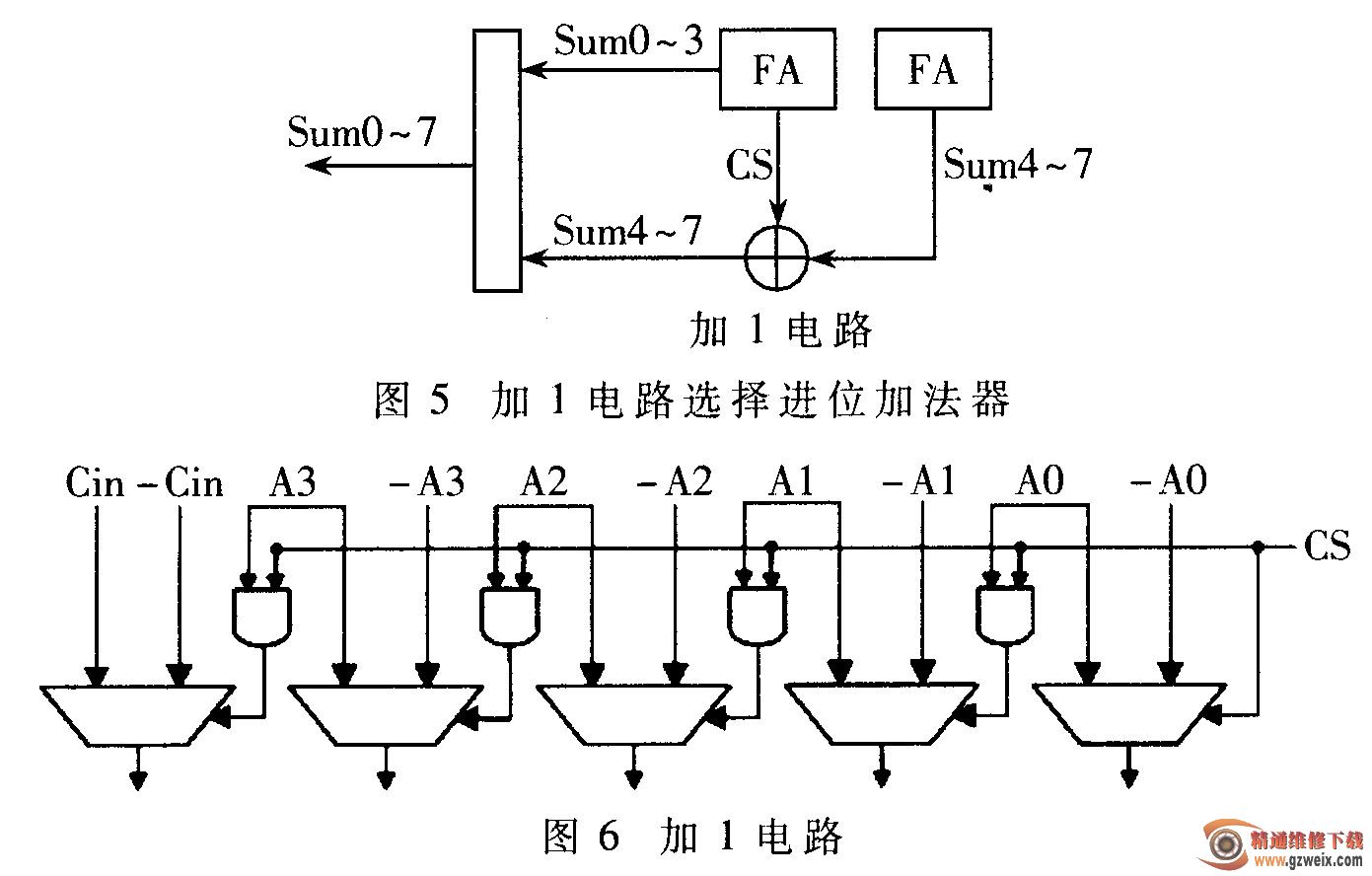

传统的进位选择加法器使用两个相同的行波法加法器计算高位的值,两个行波法加法器分别假设进位为0和1并同时进行计算,等待正确的进位到来时,再选择正确的结果输出。这样虽然可以缩短等待时间,但是占用面积较大。本文采用加1电路的选择进位加法器,如图5所示。高位加法器以固定进位为0进行计算。若正确进位为0,则加1电路不必进行计算,直接输出结果;若正确的进位为1,则将此结果加1,得到进位为1的结果。加1电路如图6所示,其中CS表示低位进位。如此,计算阵列的面积和功耗将会降低很多,处理速度也较快。

2.4存储器设计

由于当前像素直接存放在阵列寄存器中,所以不需要设计缓冲器。考虑到参考块一共有47x47个像素,且每个周期需要配合计算阵列蛇形输人数据,因此采用片上RAM来缓存参考数据。将参考块分为6个区域,每个区域大小为8 x47个像素,用RAMO-RAMS来标识,如图7所示。设计使用双端口RAM,利用奇偶地址,让32 bit双端口RAM相当于64 bit单端口RAM。由于相邻宏块的搜索区域重叠部分占整个搜索块的三分之二,按照本文的存储器设计,当进行下一个宏块的运动估计时,不需要更新整个参考块的数据,只需更新其中两个区域的数据即可,进一步减少了存储带宽,提高了数据的重用率。