摘要:设计了一款带自动波特率检测且误差较小的UART模块,旨在获得良好的通信功能。该模块支持全双工的串行数据传输和红外通信功能,且支持DMA模式以减少CPU的占用时间。UART的发送和接收通道各有一个FIFO模块。最后,利用Verilog语言的硬件实现方法在FPGA平台上进行了验证。

通用异步收发器UART(Universal Asynchronous Recei-ver/Transmitter)是串行通信的重要组成部分,其基本功能是实现数据的串行化/反串行化和错误校验,这也是所有的UART设计都能实现的基本功能,但是其他各种功能都兼顾的设计非常少。参考文献[1]设计了一个在MCU中运用非常广泛的UART接口,其功能比较全面,但是波特率产生器采用整数分频的设计,导致系统只有在特定系统时钟、特定波特率的情况下误差才会比较小,不能满足高波特率和非标准波特率的要求;设计的UART IP基本功能良好,但是不支持红外、自动波特率检测等功能;的设计只支持中断模式,不支持DMA模式,不能满足大量数据高速传输的需求,且中断总是打断CPU的操作,效率较低。本文提出了一种多功能UART模块的设计,并利用Verilog HDL语言进行实现。本设计能满足多模导航基带芯片中的不同需求(如相关器数据的传输等),同时降低误差,保证卫星数据的正确性。

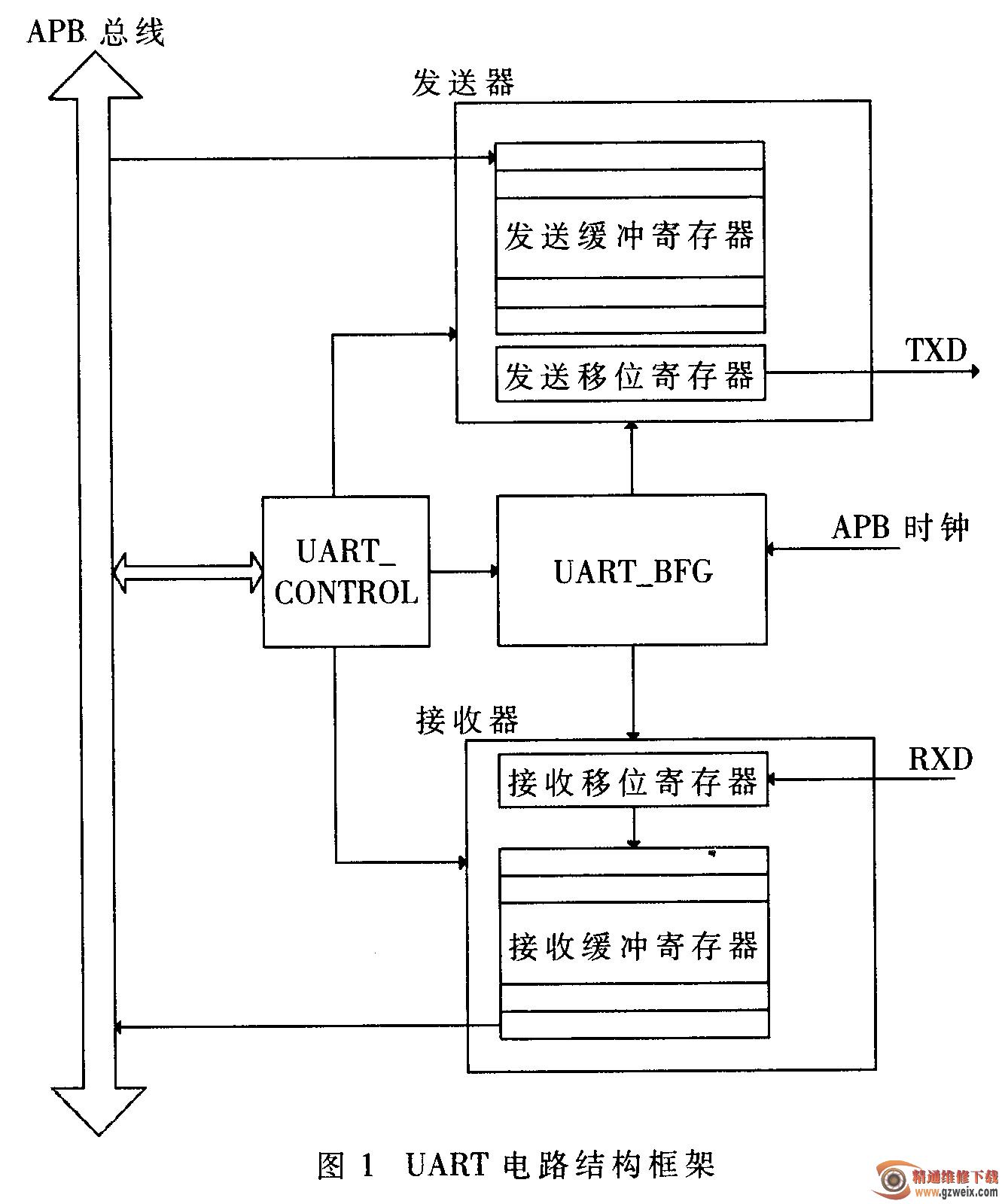

1 UAR丁电路主要模块设计

本设计采用标准的UART传输协议,字符帧由起始位、数据位、奇偶校验位和停止位四部分组成。 UART电路包括UART总控模块UART CTRL、波特率产生器UART BFG、数据发送模块TRANSMITTER、数据接收模块RECEIVER和FIFO模块,其总体结构图如图1所示。

1.,接收模块

串行数据帧和接收数据时钟是异步的,由逻辑1跳变为逻辑可视为一个数据帧的开始,所以接收器首先需要判断起始位,常用的方法有三倍速采样法和起始位中断捕捉定时采样法。据经验可知,数据的中间采样值可靠性较高,可以采用中间时刻采样法,并且,接收和发送单元的数据采样率为波特率的16倍,可降低由于时钟不匹配引起的误采样。接收器采用状态机实现,状态机的描述如下:

(1) RX_IDLE:当UART接收器复位时,FSM处于这一状态。在该状态中,状态机一直等待RXD电平跳变,即出现下降沿。检测到起始位后,进人RX_START状态。

(2) RX_START:在该状态下,在采样时钟的上升沿对URXD低电平进行计数。当计数为8(即确保在起始位的中间点)时,转到RX_ DATA状态;如果逻辑零的个数少于8,则认为是毛刺,跳回RX_IDLE状态。

(3) RX_DATA:在该状态下,每隔16个采样时钟采样1 bit串行数据,接收8 bit异步数据并进行串/并转换。同样是对采样时钟的上升沿进行计数,当计数值为16时进行数据采样。如果起始位为16位,则可以保证数据位都是在中点处被采样,同时进行串/并转换。当探测已经接收到相应位的数据后,进人奇偶校验状态。