(4)RX_PARITY:该状态的主要功能是奇偶校验,通过对实际接收到的数据的奇偶性与发送过来的奇偶校验位进行比较,判断奇偶校验错误状态。

(5) RX_STOP:对停止位进行采样,并且判断停止位是否为1。若停止位不正确,则帧错状态位置 1。

将接收到的数据和错误状态数据一起写人到接收FIFO中。接收到错误的数据后不马上产生错误中断,一旦数据被读出,此时错误状态也一起被读出,立即产生错误中断。

1.2发送模块

发送器实现的功能是将输人的8 bit并行数据变成串行数据,同时在数据位头部加人起始位,在数据位尾部加奇偶校验位和停止位。发送模块的设计比较简单,其状态机与接收模块相对应,在此不再赘述。

1.3波特率产生模块

波特率发生器一般采用分频器实现,传统的采用整数分频器实现的误差在某些系统时钟下超出了可控范围,如在参考时钟为16.37 MHz、波特率为460 Kb / s的情况下,误差达到了11.2%,会导致数据传输的错误。因此,本设计采用小数分频器实现相对准确的波特率。另外,在收发的过程中,可以改变波特率寄存器的值,但实际波特率的改变发生在当前帧传输完成之后。波特率产生模块的电路结构图如图2所示。

小数分频的实现方法有很多,但其基本原理是一样的,即在若干个分频周期中采取某种方法使某几个周期多计或少计一个数,从而在整个分频周期内总体平均分频数为小数分频。

通过采用小数分频,大大降低了实际波特率与要求波特率之间的误差。在正常情况下,误差不应超过2%,如果超过了,则需要相应地提高系统时钟来降低误差。表1列出了19.2 MHz情况下的整数分频和小数分频波特率误差对应表,可以看到采用小数分频的波特率误差明显较小。

在本设计中,发送器、接收器和波特率产生模块是主要模块。FIFO(先进先出)模块是数字电路设计中比较常用的模块,本文复用了通用的FIFO模块,在文中就不再赘述。DART的控制模块主要负责对寄存器的相关操作,通过APB总线实现,其电路设计比较简单,也不再赘述。

2 UART模块的其他功能

2.1自动波特率检测

UART接收通道在接收数据之前,如果发送端的波特率不清楚,可进行自动波特率检测实现方法是:发送端间隔发送检测字,间隔时间为传输一帧所需的时间。接收方UART根据start位来确定是否有数据在传输,当其检测到下降沿时就进入RX START的状态中,在波特率不明确的情况下,并不产生采样时钟,用PCLK进行采样计数。由于start位为1 bit,根据计数值可知这1 bit所占用的时间。如果接收数据完成后,接收到的数据是约定值,则证明波特率检测成功,可以将检测到的值存储于寄存器中。自动波特率检测原理公式如下:

1 /baudrate=count x(1 /PCLK) (1)

根据式(1)可得发送端的波特率。实现自动波特率检测无需专门的模块设计,在接收器模块内就可以实现。

2.2自检测模式

Loopback(自检测)模式是UART内部的一种自测功能。当UART出现问题时可以先自测,将控制寄存器中Loopback位使能,UART可以将内部的发送(TXD)和接收(RXD)连接在一起,确定内部的数据通路没有问题。

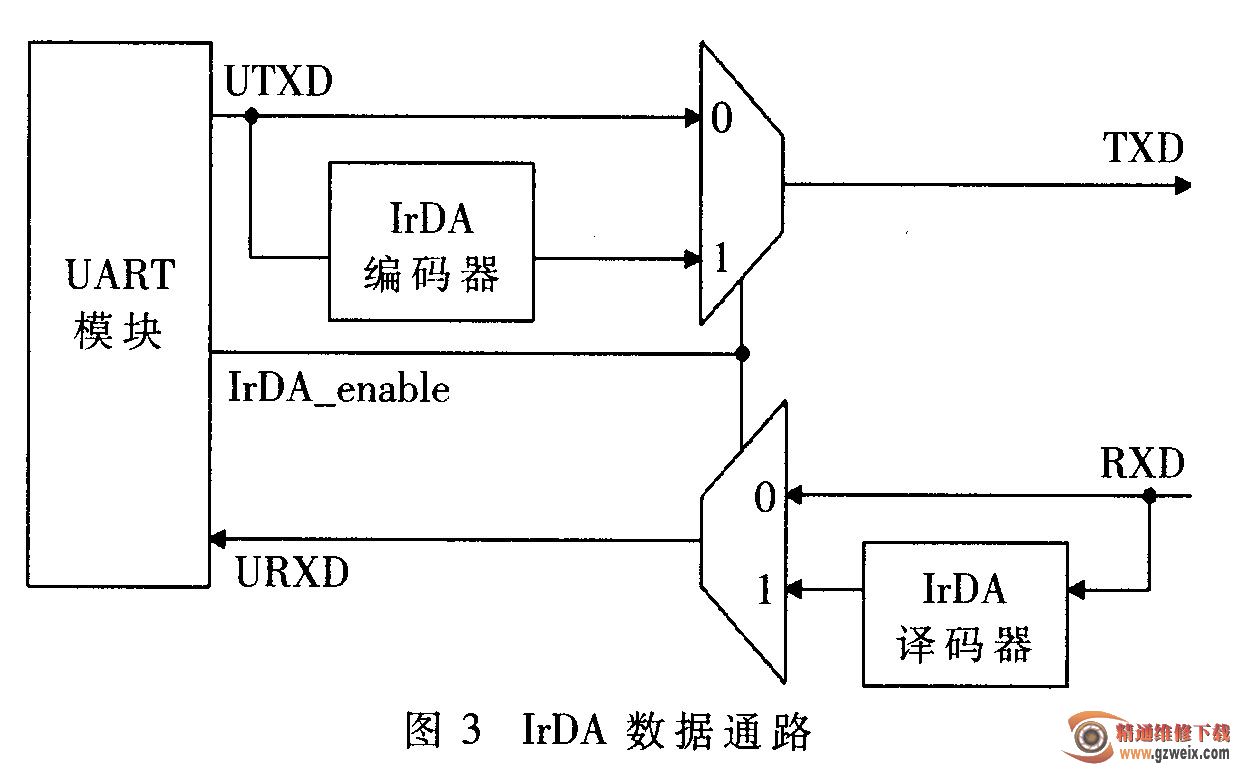

2.3红外传输功能

本设计的UART支持IrDA 1.0协议,所以使用红外时最高波特率为115.2 Kb/s。通过寄存器的红外控制位选择红外使能,可以实现红外脉冲。IrDA数据通路如图3所示。

2.4 DMA模式

本设计UART不仅支持查询、中断模式,还支持DMA模式以提高连续传输的能力,能够高效地传输基带芯片相关器中的大量数据。CPU除了在开始和结束时处理中断外,在传输过程中也可以进行其他工作。