3仿真验证和综合结果

3.1仿真验证

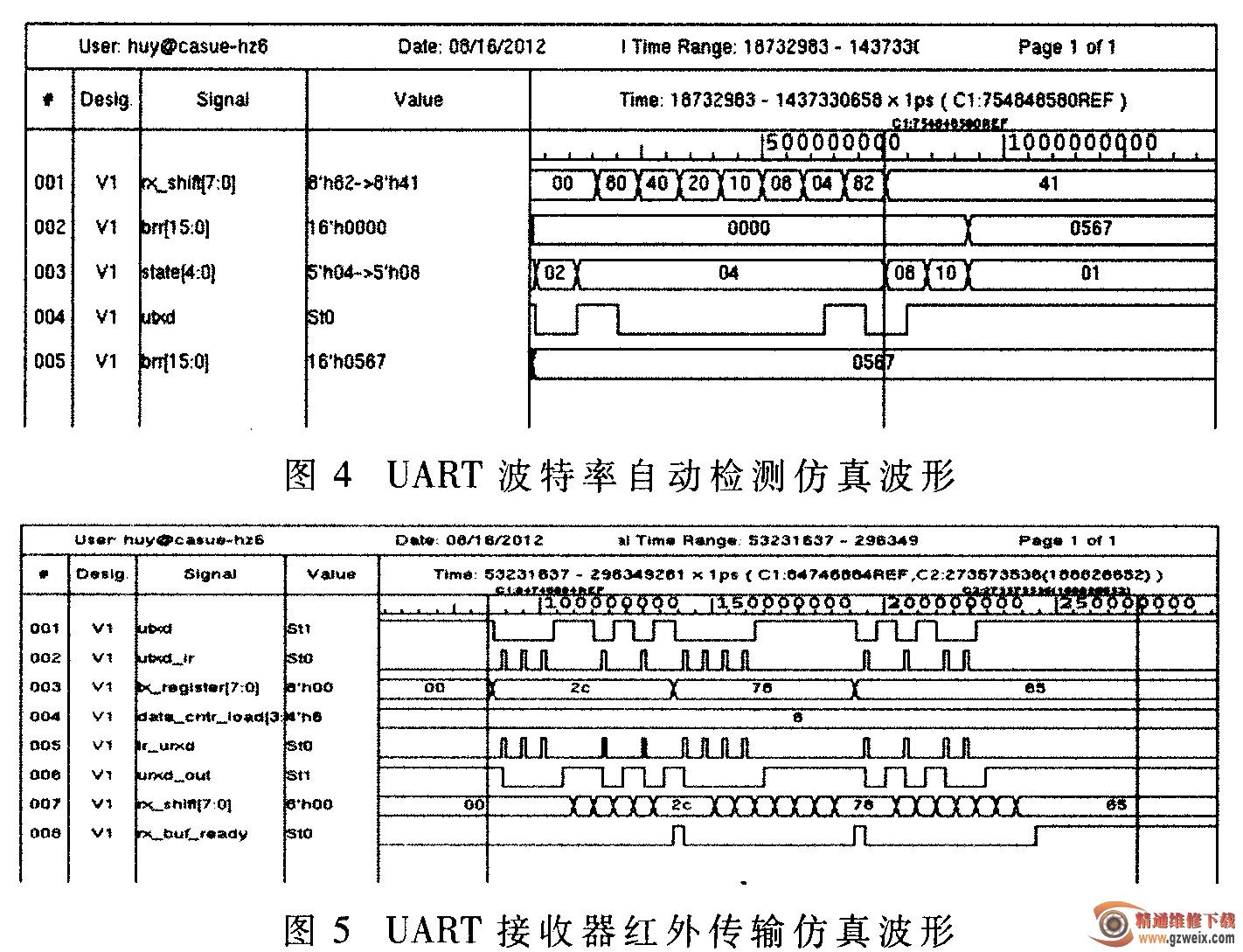

本文采用Altera公司EP3SL150F1152的FPGA芯片进行实测,使用VCS仿真工具,并利用VERA语言和Verification IP进行验证。仿真结果如图4、图5所示。

图4是波特率自动检测的仿真波形。002号波形是未知波特率的接收端波特率产生器的分频值,在未知的情况下为0 ; 005号波形是发送端波特率产生器的分频值,为567H。从002号波形的变化可以看到,发送端发送检测字41H,接收端在接收完一个检测字41H后,可计算出波特率分频值为567H v 001号波形是接收端的接收移位寄存器,将串行数据转化为并行数据,接收完成后得到41H,也证明了数据的正确传输。这种波特率检测的方法迅速准确,一般情况下发一次检测字就能检测出发送端的波特率。

图5是数据红外传输的仿真波形。编码模块将待发送的001号波形编码成符合红外协议的002号波形发送出去,接收端接收到005号波形要经过译码模块译码成006号波形输出给接收器。由图中可以看到,发送寄存器发送了3个值2cH, 78H , 65H,在经过编码、译码模块后,接收器能够接收到正确的值。008号波形中高电平脉冲表示一个数据接收成功;007号波形接收移位寄存器中的数据正是发送端发送的3个值,证明数据能够正确传输。本设计支持协议中5 bit, 6 bit, 7 bit, 8 bit数据的传输,图5中采用的是6 bit数据位。

3.2综合结果

DART接口包括DART接口模块(接收和发送模块)、两个FIFO模块(深度为32、宽度为8), UART波特率产生模块和UART控制模块,在0.18 [Lm CMOS的工艺下用Synopsys的Design Compiler对模块进行综合,将UART接口的输人时钟PCLK设置为100 MHz,模块总面积为19 620.7 μm2,约合1962逻辑门、7 848个晶体管。

本文提出了一个功能全面的UART IP核的设计,并采用Verilog HDL语言实现。在与PC机的长时间串口通信实验中能够正确进行传输,在不同的波特率设置下都能正确工作。同时,用示波器观测传输波形可知,波特率误差小于1%。设计完成后,在VERA平台上进行了仿真验证,最后下载到FPGA平台上实现,与PC的串口相连,采用串口大师软件进行实测,其在全双工模式下也能正常工作,实测的结果显示其性能和功能都能满足要求。