AD9854的相位输出是连续的,每一次的相位控制字变化都会在原有相位的基础上进行加减。因此,在每次输出相干波形之前,要求对两片AD9854进行复位或重新设置初始值,以保证两路输出信号初始相位已知。当新的数据送到相位累加器后,可根据它们的相位控制字计算两路信号的相位差。

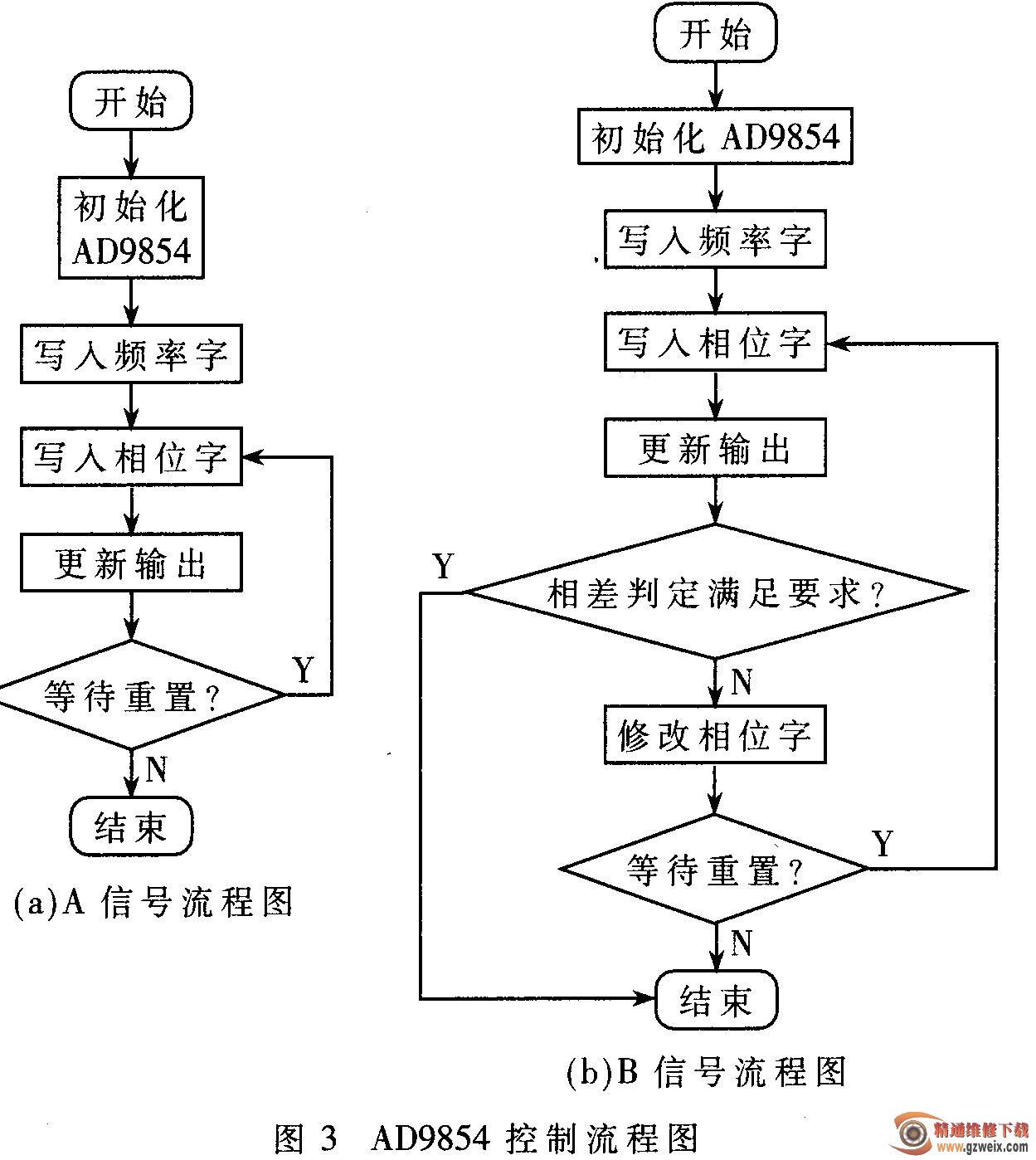

在具体编程控制中,可采用以下简化方法进行处理:固定其中一路信号(A信号)的相位,可通过调整另一路信号(B信号)的相位控制字来设定两路信号的相位差。相位控制字由FPGA先写人两片AD9854的缓存寄存器中缓存;经过一定时延后,FPGA发送更新命令将两路信号的相位字和频率字同时更新并寄存在AD9854的相位寄存器和频率寄存器中;最后,由FPGA通过两路信号的相位控制字计算相位差,如满足要求,则确定两路信号输出,否则重新设定B信号相位字。其控制流程图如图3所示,其中图3 (a)为A信号的流程图,图3(b)为B信号的流程图。

2.2控制模块

FPGA逻辑控制是实现双路信号同频相位差可调的核心,共有3项任务:接收键盘的命令;配置AD9854实现波形输出;通过相差检测技术实现双路信号相位差精确控制。本设计FPGA选用Cyclone II系列的EP2C8。EP2C8器件提供了全局时钟网和具有片内、片外能力的PLL,可实现完整的系统时钟管理;经优化后可实现最小的延时偏移,为器件内的所有资源提供精确的时钟和复位信号。另外, EP2C8器件包括嵌人式18 x 18 bit乘法器,可轻松完成两路信号的相差检测。

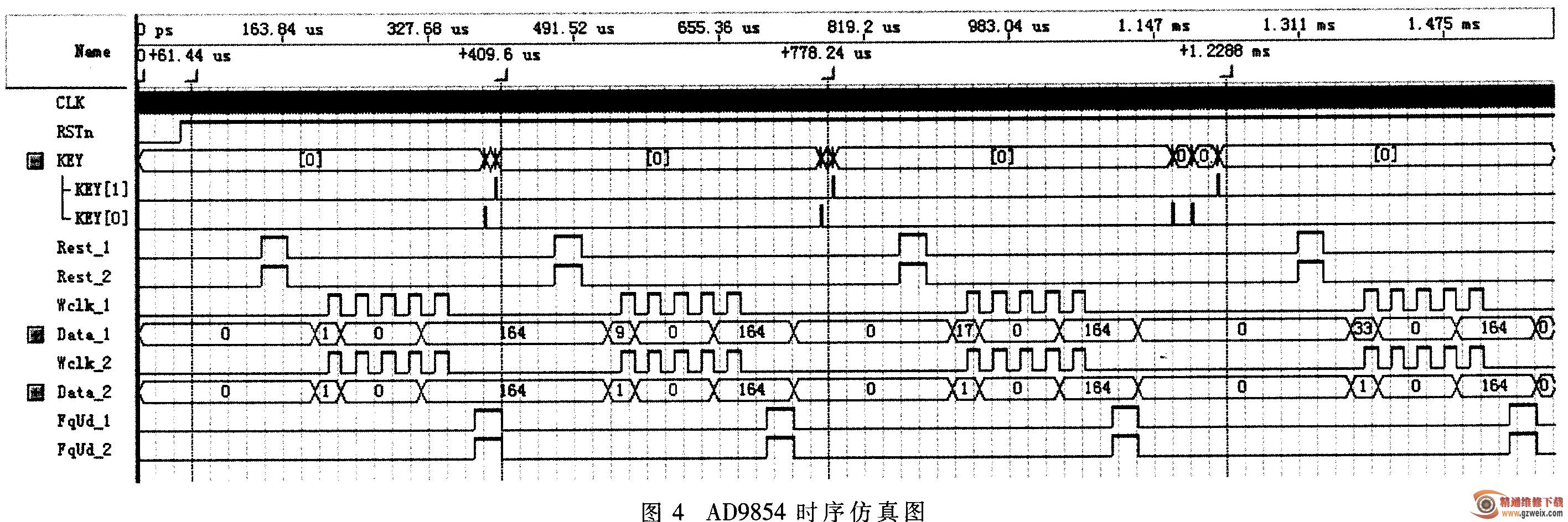

FPGA逻辑设计的重点在于对两片AD9854的时序控制。同时,写时序时要注意控制命令的顺序及命令之间的合理延时。在Quartus II中完成的AD9854时序仿真图如图4所示,图中模拟了两个输入按键。其中KEY[0]代表相位增加按键,每按一次相位控制字加1;KEY[1]代表同步更新按键,每次相位字改变后需按一次KEY[1]键才能同步更新输出。FPGA逻辑设计的具体步骤为:

第一步,初始化。在第50 μs时,RSTn由低电平变高电平,系统开始工作;延时一段时间后,同时给两片AD9854提供一个复位信号(在图4中第150 μs附近的Rest _1和Rest_2);复位完成后,在参考时钟控制下通过Data_1和Data _2端子同时对两片AD9854写人初始相位控制字;延时一段时间再写人频率控制字,启动FgUd_1和FgUd_2命令更新芯片的相位和频率。

第二步,调节相位差。频率始终保持不变,固定第二片AD9854_2,的相位字;通过KEY [0]和KEY [ 1]按键调整第一片AD9854_1的相位控制字,在400μs、 770μs和1.2 ms附近分别进行设定。Data_I的相位数据随之发生变化,而Data _2的相位数据不变。由于Data _2的初始值已知,可根据Data _1相位控制字的变化计算两路信号的相位差。

从图4中也可以看出,FPGA在控制两片AD9854时,时序设置非常重要,故要求控制信号必需同步,即使较小的延时也将导致结果不准确。