・上一文章:分析及排查涡轮增压系统故障的方法

・下一文章:RFID动态帧时隙防冲撞改进算法研究

Shift-xR状态测试数据或测试指令传输的操作流程如图4所示,图中ram address为缓冲器地址,ram reload表明装载缓冲器,test_ data为测试数据或测试指令,shift cnt为移位计数器。据此设计一个8x8的测试缓冲器,通过测试数据管脚并行接收PC机的测试数据或测试指令,在数据传输过程中通过TDO串行输出。

2.2.3选择机制控制模块设计

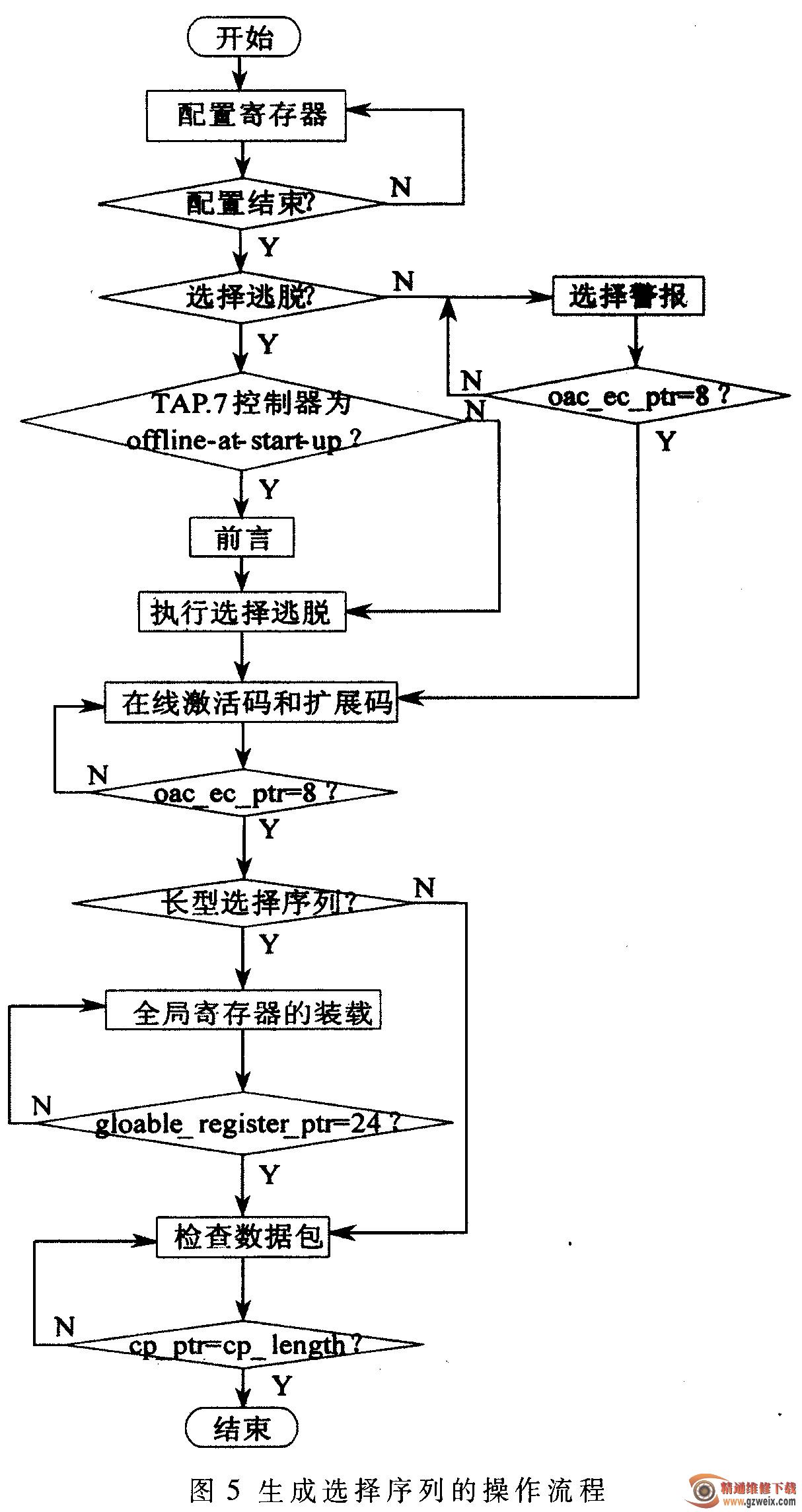

选择机制控制模块实现T0层的选择序列。首先TMS(C)与TCK(C)信号产生相应的逻辑序列实现选择逃脱或警报初始化选择序列。初始化选择序列后,通过TMS(C)在TCK(C)下降沿产生指定的逻辑序列生成选择序列。

生成选择序列的操作流程如图5所示。

2.2.4其他控制模块设计

其他控制模块设计过程类似,命令控制模块实现T1层的控制器命令,以TAP. 7控制器状态机为基础设计一个模块状态机,产生所需要的测试信号实时控制待测芯片,依次实现待测芯片的ZBS以及控制器命令。

Star -4控制模块实现T3层的Star -4测试信号,以TAP. 7控制器状态机为基础设计一个模块状态机,产生需要的测试信号实时控制待测芯片,在允许停泊的状发送SSD指令,选择目标控制器传输数据。

Star - 2控制模块实现T4层Star - 2测试信号,以TAP. 7控制器状态机为基础设计一个模块状态机,产生所需要的测试信号实时控制待测芯片调用高级协议,在Star-4控制模块的基础上实例化调用高级扫描生成模块,产生Star-2扫描拓扑测试信号。