摘要:在深入研究IEEE 1149.7标准的基础上,针对测试问题设计了CJTAG测试控制器,实现了T0,T1,T3和T4层级的主要功能。对该控制器的各个功能进行了仿真验证。结果表明该控制器产生的测试信号符合IEEE 1149.7标准的规定,能够控制待测芯片实现相应的测试功能,取得了较好的测试效果。

随着微电子技术、表面贴装技术和印制电路板制造技术的不断发展,单芯片多核设计、片上系统和叠层裸片技术等成为主流技术。现有的边界扫描测试方法(JTAG)已很难满足来自于测试、调试和功能等多方面的挑战:测试时需同时对多个测试存取端口(TAP)进行控制和扫描;调试时需缩短扫描链长度及支持调试数据的传输;功能上需减少测试引脚并且实现更低的功耗。在此背景下,可测试性总线标准委员会于2009年表决通过IEEE 1149.7标准,提出了紧凑型边界扫描技术(CJTAG) 。 CJTAG在兼容IEEE 1149.1标准的基础上增加了新特性,完全满足现阶段芯片设计过程中测试与调试的新要求,且不影响目前市面上基于IEEE 1149.1标准设计的芯片进行测试与调试操作。

标准公布以后,在国内外电子业界引起了高度关注。CJTAG的研究主要包括两个方面,一方面是设计支持CJTAG测试的电路芯片:充分利用待测芯片的紧凑型边界扫描测试逻辑结构,提高电路芯片的测试与调试的效率,国内徐志磊等人对此研究设计和验证了CJTAG接口;另一方面是对支持CJTAG测试的电路芯片设计相应的测试系统:产生符合IEEE 1149.7标准的测试信号。本文主要研究后一问题,即在IEEE 1149.7标准所提出的边界扫描测试的基础上,研究组建1149.7边界扫描测试系统的设计方法。

1 IEEE 1149.7标准简介

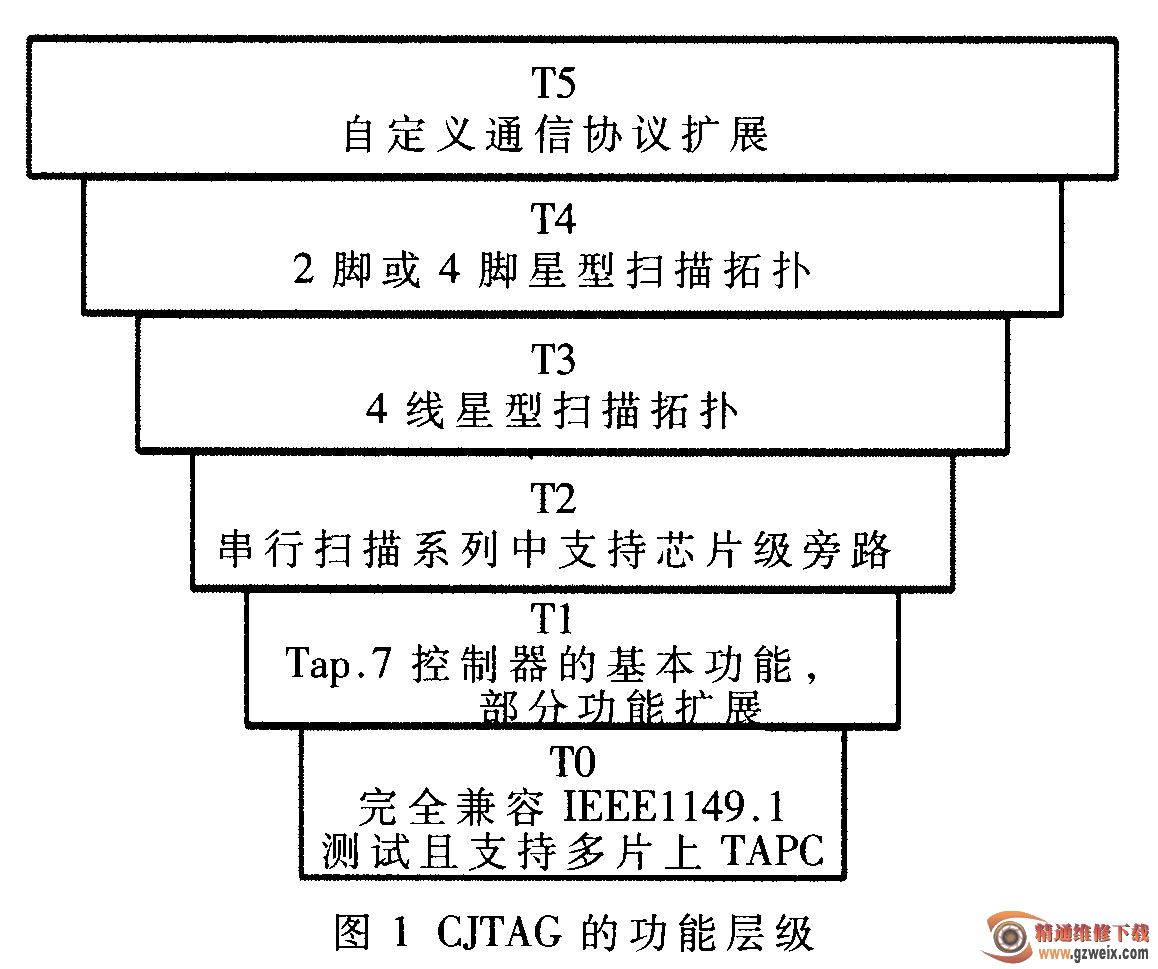

IEEE 1149.7标准以IEEE 1149.1-2001边界扫描标准为基础,提供可升级的测试方法满足集成电路种类繁多及功能复杂的需要,从功能上划分为T0-T5六层,每一层都在它上一层的基础上增加新的功能,如图1所示。

T0层确保符合IEEE 1149.1标准测试基础构架的可行性,支持多片上TAPC(测试存取引脚控制器)串行结构,可通过选择序列控制共享DTS的技术分支。T1层用零位DR扫描(ZBS)设定TAP. 7控制器的状态,在不影响TAP. 1控制器的前提下实现控制器命令。T2层通过芯片级的旁路扫描路径大幅缩短扫描链从而提高调试芯片的效率。T3层增加了4线星型(Star-4)扫描拓扑,可直接对TAP. 7控制器进行寻址。T4层实现了质的飞跃,增加的2线星型(Star-2)扫描拓扑将TAP. 7所需要的引脚数从4减少为2。 T5层支持自定义的通信协议,且使用8个数据通道支持后台数据的传输,使测试引脚能同时进行待测芯片的调试与基本操作。

IEEE 1149.7标准根据测试与调试所需引脚数规定了标准协议和高级协议:标准协议指使用TCK,TMS引脚控制TAP控制器(支持IEEE 1149.x标准的TAP控制器)的状态进程,使用TDI, TDO引脚完成测试数据的传输;高级协议指使用TCKC与TMSC引脚不仅能控制TAPC的状态进程,而且还能完成测试数据的传输,TDIC和TDOC引脚可以闲置或做其他功能使用。IEEE 1149.7标准规定CJTAG的T4和T5层使用高级协议。根据IEEE 1149.7标准,T2和T5层的功能在调试方面更具优势,本文所设计的CJTAG测试控制器主要解决待测芯片的测试问题,故本文重点实现支持CJTAG的T0,T1、 T3和T4层的测试。