・上一文章:用信道仿真器全面测试LTE系统

・下一文章:基于Asterisk的电话会议系统研究与设计

I2C总线控制读/写操作过程如表2、表3所示(S:开始,Sr:重开始,P:停止,-S:从设备,-M:主设备,W:写位,R:读位):

在设计中主要实现以下四种功能:开始条件功能、字节发送功能、应答条件功能和停止条件功能。四种功能信号的时序和数据总线传递如图2、图3所示。

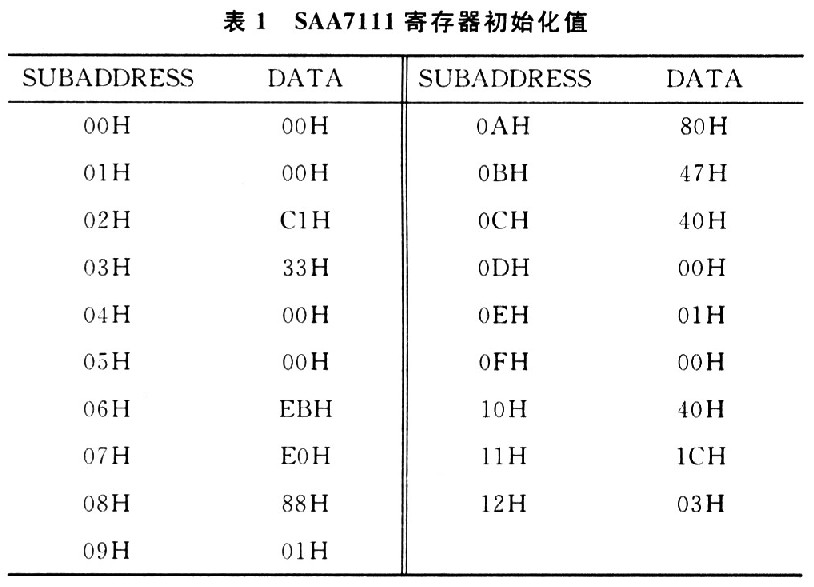

为了完成上述要求和功能,本文采用VHDL语言编写逻辑的方法来模拟I2C总线接口时序逻辑,配置数据可以由主机发送,也可以预先存放,同时用VHDL编写时序逻辑对SAA7111进行初始化配置。根据设计要求,在不同的进程下对串行时钟线(SCL)和串行数据线(SDA)进行设计。时钟信号源采用10 MHz的晶振,分频后作为进程激励信号,基本能够满足SAA7111芯片的数据率要求。但如果在一些更高速的情况下,需要快速通过I2C总线对被控器件进行设置,这里只需将行时钟线(SCL)和串行数据线(SDA)的频率进行修改即可,其接口控制如图4所示。