3 数据缓存模块设计

数据缓存器使用Ahera公司的FLEXlOKE系列CPLD。该设计利用FLEXlOKE器件实现高速FIFO,由于作为数据缓存的FIF0的输入输出时钟频率不能相同,所以必须使用双时钟FIFO。且该类器件用低电压供电,大大降低了系统功耗,提高了系统的灵活性和可靠性。

本文所介绍的系统使用VHDL硬件描述语言来对FLEXlOKE进行编程,编程环境为MAX+PLUSⅡV9.6扳本。

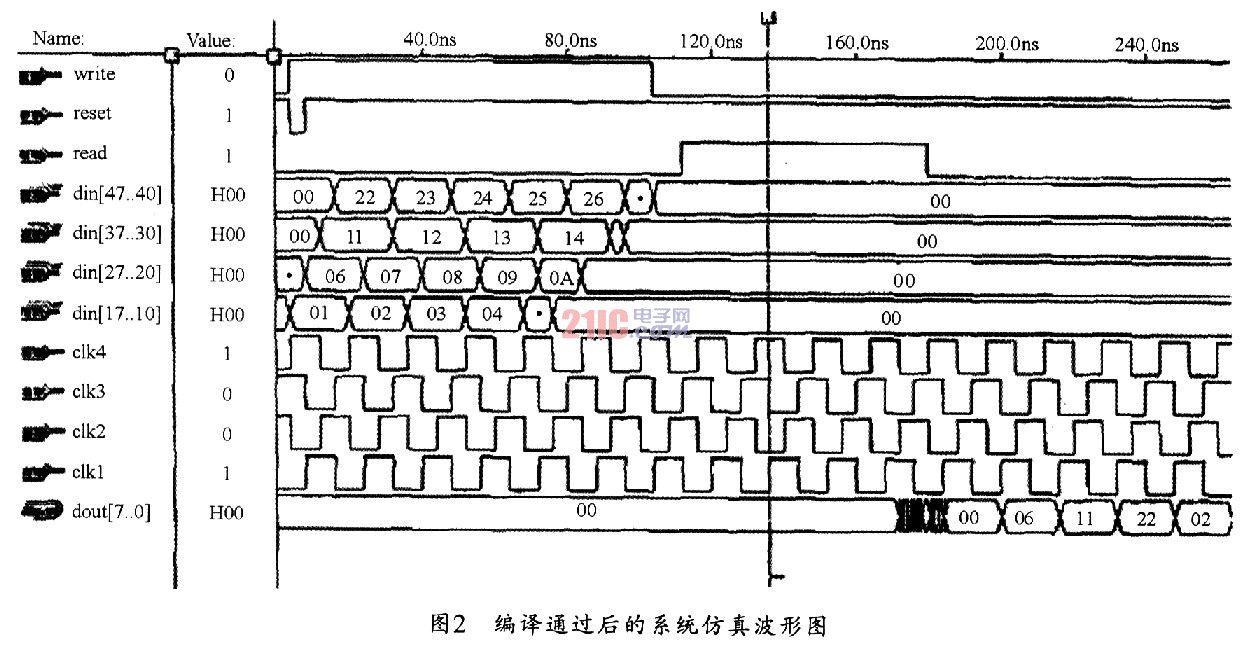

VHDL编程采用模块式设计。首先建立4个模块,即FIF0、MUX、counterl、counter2。其中的FIFO既可以调用lpm-FIF0(dualClock)来修改其中的一些关键参数以符合要求,也可以手工编写程序实现,这里采用调用宏模块的方式。值得注意的是,FIFO的输入输出时钟频率不同,因此必须采用双时钟FIF0。MUX、counterl、counter2是配合FIF0使用的多路复用器和分频器(计数器),均应手工编写其源程序。几个子模块完成以后,要新建一个总的系统模块(system)来调用子模块,以在system模块中完成系统端口的定义以及各个子模块之间的逻辑关系描述。这种设计有利于逻辑设计的集成化,从而为后续的改进提供方便。图2为编译通过后的系统仿真波形图。

4 结束语

本文以DRFM设计为核心,着重介绍了DRFM的数据采集前端的设计思路和方法。在超高速数据采集领域,数百兆乃至1 GHz的采样速度非但在国内,即就在国外也是电路设计的难点。使用基于SRAM的CPLD可以有效避开使用高速FIFO作为缓存器带来的高功耗、高开销的影响。数据缓存可以在一个片子内实现,降低了硬件的复杂度,减小了系统的功耗。更加值得关注的是,这类CPLD具有icr,即在电路可重配置,可以通过对其编程的方法其修改电路功能,这样就为后续的系统改进打下了良好的基础。