・上一文章:大信号检波器电路--均值包络检波器

・下一文章:大信号检波器电路--串联型二极管峰值包络检波器

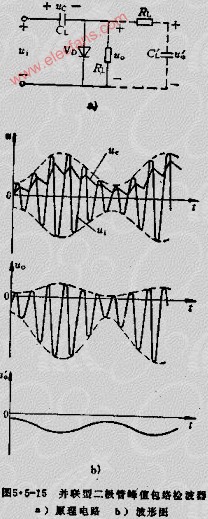

并联型二极管包络检波器

这种检波器的原理电路见图5.5-15A。图中CL是负载电容,RL是负载电阻,RL与二极管VD并联,为VD电流中的平均分量提供通路。鉴于RL与VD并接,故将这种电路称为并联型电路。

并联型电路具有与串联型电路相同的检波过程。当VD导通时,U1向CL充电,充电时间常数为RDCL1当VD截止时,CL通过RL放电,放电时间常数为RLCL。由图可见,RL上的电压UO有很大的高频成分若加一切由RLCL组成的低通滤波器(图中用虚线表示)即可取出输出电压UO。

并联型电路具有电压传输系数比串联型电路低(由于低通滤波器的RL与CL两端所接电阻的分压损失),输入电阻R14也较低(R1D≈1/3HL)的缺点。其优点是CL可以兼有隔直流电容的作用,电路较为简单。故并联型电路一般用于需要、隔高频信号源中所含直流电压的电路中。