・上一文章:如何用EL34制作的合并式电子管功放

・下一文章:推拉输出电路中的静态功耗

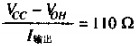

HCT总线驱动器上端的输出电阻:

RC上升时间

当输出从低电平转换到高电平时,充电时间常数约等于驱动器输出电阻乘以输出负载电容。

TRC=(110欧)*(220PF)=24NS

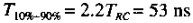

数值TRC是输出端电压从低电压从低电平状态升至高电平的63%时所需的时间。升至高电平的90%时所需的时间是TRC的两倍多一点。一个简单RC电路的10~90%上升时间是RC乘积的2.2倍:

多么令人惊奇!我们本以为驱动器的最大传播迟为9NS,而实际的延迟变成了53NS!如果该总线运行在33MHZ上,数据信号在下一比特到来前将没有足够的时间上升或下降到满幅值。我们把总线频率降至16MHZ,以便让数据单元获得更多的间隔时间。

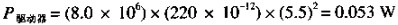

每个驱动器的功耗

VCC=5.5V(最差的情况时的供电电压)

C=220PF(负载电容)

F时钟=16MHZ(降低后的时钟频率)

F数据=8MHZ(最差的数据周期,是时钟频率的1/2)

计算每个驱动器的功耗:

再乘以单个器件封装内的驱动器数目8,即可得到一个封闭器件的总功耗:

P总=8*0.053=0.424W

一片20个引脚的塑料封装芯片消耗的能量还会更多。上面例子中的总线设计是不切实际的,因为上升时间太慢,并且驱动器的功耗太高。我们必须将该总线的工作频率降低到16MHZ以下。