・上一文章:如何用EL34制作的合并式电子管功放

・下一文章:推拉输出电路中的静态功耗

设计者经常仅仅根据所接负载的直流输入电流要求,冒险使推拉输出电路的负载达到它的最大直流扇出能力。特别是当设计CMOS总线时这一想法尤其具有诱惑力,因为此时理论上的扇出能力是无限的。实际上重负载的总路线结构会带来两个缺点,上升时间将会减慢,而且驱动器件的功耗将会提高。

下例是一个重负载CMOS总线的实际上升时间和功耗计算的例子。

例:CMOS总线的性能

我们正为一台并行计算机的共享存储器子系统构造一个大型总线,如图2.8所示。总线连接着20个小的CPU,其中任何一个都可能存取这个8位的随机访问存储器(RAM)。整个系统装配在一个大的电路板上。

该总线是通过阻抗可控的50欧印刷电路走线来实现的,走线长度为10IN。图2.8显示出总线的传播长度远远小于74HCT640门电路上的上升时间,因此在总线的两端都没有使用端接器。

根据直流扇出系数,我们预期每个总路线驱动器应该能够很容易地驱动其他20个电路。已知每个收发器的最大传播延迟为9NS,我们计划使总线运行在30NS的周期上(33MHZ)。

为了检验这一设计,计算出每一条印刷线路负载电容,并分别与三态输出的驱动阻抗相比较,计算出总线的RC上升时间。最后计算每个驱动器内的功耗。

负载电路

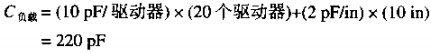

当每个驱动器转换到关闭(OFF)状态时,仍然存在负载电容。每个驱动器的这一I/O负载电容在手册中都被制造商标明为10PF。我们有20个负载,所以负载电容总共为200PF。加上底板印刷线路的电容2PF/IN,可以得到:

74HCT640的输出电阻

在SIGNETICS的高速CMOS数据手册上列出了以下指标(两个驱动晶体管中上端的情况是最差的):

VCC=4.5V

VOH=3.84V

I输出=6.0MA