跳频通信 系统作为扩频通信体制中的一种重要类型,以其出色的抗远近效应、抗干扰能力,在军用、民用通信领域得到了广泛应用。跳频通信方式是指载波受一伪随机码的控制, 不断地、随机地跳变,可看成载波按照一定规律变化的多频频移键控(MFSK)。跳频通信的频率受伪随机码控制不断跳变,跳频图案可以设置几千乃至上万个,收发两端只要跳频图案一致,跳频时间同步,就可在信息传输过程中不断跳变空间频率信道,实现跳频通信。

近年来随着半导体工艺和计算机技术的发展, DSP (Digital Signal Processor)、 FPGA (FiELD Programmable Gates Array)等现代信号处理芯片越来越成熟和普遍使用,以前只能理论研究的跳频技术有了实现的可能。

1 基于FPGA/Dsp的跳频系统硬件架构

本跳频通信系统的发射系统如图1。信源信息进入dsp进行信道编码;随后dsp根据编码结果使能FPGA控制 DDS 在中频段产生跳频信号;最后混频器把信号频率搬移到射频上,经过高频放大器放大后发射。

接收系统如图2。天线将接收到的信号经过高频放大器放大后,与第一本振混频,产生第一中频信号;DDS受dsp控制,作为第二本振,与接收到的跳频信号按相同规律跳频(但频率相差一个中频),至此得到了固定中频,完成解跳;随后,对信号进行中频采样,在数字域中利用正交NCO(NCO位于FPGA中,受dsp控制)实现数字解调;得到的结果在dsp中进行信道解码,恢复原始信息,送到信宿。

可以看到本跳频系统中,FPGA是硬件逻辑的载体,完成基带信号采样后的混频、滤波等操作及对DDS、ADC等外部逻辑的控制;dsp控制FPGA内部逻辑以及DDS、ADC等逻辑单元完成跳频通信系统基带部分的发射与接收及其一系列计算任务;高精度时钟源为整个系统提供时间基准,经过dsp、FPGA、DDS等器件内部锁相环倍频,为各器件提供主时钟。

2 dsp与FPGA之间的数据通信设计

dsp与FPGA之间的接口如图3所示。

FPGA上的逻辑设计采用了OnChipBus+UserLogIC的SOPC设计思想。其中OnChipBus采用Avalon总线。Avalon交换结构是ALTEra公司提出的一种在可编程片上系统中连接片上处理器和各种外设的互联机构,是一种同步总线,包含完善的总线仲裁逻辑,并针对自身产品进行逻辑优化,特别适合用在Altera FPGA上。但是,Avalon总线与C54x系列dsp的外部存储器异步接口时序不兼容,为此,设计了Bus Bridge模块,一边是dsp EMIF的Slave Interface,连接到dsp的EMIF,映射到dsp IO空间;另一边是Avalon总线的Master Interface,连接到Avalon总线,从而实现两种总线间数据的透明传输。

FPGA的内部逻辑采用了模块化的设计思想,每个Logic都包括AvalonSlaveInterface、RegisterFile和UserLogic三部分。其中, AvalonSlaveInterface是AvalonBus的从接口逻辑;RegisterFile是寄存器组逻辑,通过Avalone总线映射到dsp相应的IO地址空间;UserLogic用于实现用户逻辑,其功能完全由RegisterFile的内容决定。各个模块独立工作,模块之间的通信通过片上总线进行,增加了设计的灵活性,便于维护和扩展,并可以利用SOPC Builder工具完成系统的集成。

3 基于dsp/FPGA的跳频系统基带部分关键模块设计

3.1 跳频器设计

本设计选用DDS作为跳频器。DDS可以视为由NCO和高速DAC构成。NCO决定了DDS输出信号的频率范围、分辨率和相位分辨率等参数,它主要由相位累加器、相位偏移加法器和余弦表构成。其具体实现如图4。

为了适应复杂的数字接口,在FPGA中设计了DDS Controller逻辑,完成了对所有时序和数据格式的转换。dsp仅通过读写DDS Controller中的几个寄存器就可以实现对DDS的所有操作。DDS的输出端采用了互补电流输出,经过变压器耦合并通过低通滤波器后得到基频信号。

3.2 调制解调FPGA逻辑设计

本系统采用了2FSK调制方式。2FSK调制实际上就是根据二进制码流的极性输出频率f0(频点0)或频率f1(频点1),跳频通信系统根据跳频图案决定载波频率,但归根结底就是改变DDS的输出信号频率。

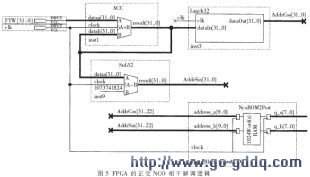

本设计采用了相干解调方式,图5给出FPGA的正交NCO相干解调逻辑图。

图5中ACC为32bit相位累加器,Sub32提供π/2的相位平移得到Q支路的波表地址,Lanch32的作用是使相位累加器的输出结果延时一个时钟周期,保持I、Q支路严格同步,因为Sub32的运算会使Q支路延时一个时钟周期。双口ROM存储余弦表,同时产生I支路和Q支路的波形。

正交NCO、数字混频器、低通滤波和采样调整模块共同构成了解调单元DeModulationLogic。

DeModulationLogic在FPGA系统中的位置如图6所示。