摘要: 针对嵌入式处理器在FPGA 中的应用现状,通过引入通用的调试模块,实现了对没有调试接口的嵌入式处理器进行在线调试的功能。所设计的调试模块通过引入专用的调试中断及与之对应的调试服务程序实现一种处理器响应断点( breakpoint) 的机制,并基于双端口RAM 中一种巧妙的地址映射机制实现同时对多行代码设置断点的功能。实际的工程应用情况表明,新的调试方法扩展了对小型嵌入式处理器进行调试的手段,明显提高了开发效率。

1 引言

在FPGA 设计中使用嵌入式处理器软核( 如MicroBlaze、PicoBlaze 等) 构成可编程片上系统( SystemOn Programmable Chip,SOPC) ,相比于ASIC 具有更好的可修改性和可维护性,得到了普遍的应用。由于ARM,MicroBlaze 等大型处理器内核具备调试接口,在与之对应的调试模块配合下,调试软件可以通过JTAG 接口实现: 执行到断点处挂起、单步执行、查看处理器内部状态、查看和修改Memory空间中的数据等基本的在线调试功能。上述基本的在线调试功能对嵌入式系统的调试具有重要意义。

对于PicoBlaze 等占用资源少、设计开发简单的小巧型处理器,一般不具备调试接口,然而在SOPC系统设计中经常需要使用上述处理器。使用上述处理器时,由于没有调试接口,属于大型处理器的标准高效的调试机制不再能够使用,因此通过指令集仿真( ISS,Cycle - accurate Instruction Set Simulation) 和利用仿真工具对含有处理器的系统进行软硬件协同仿真是确保设计正确性的重要途径。然而在诸如接收机基带信号处理等系统的设计中,仿真所用的测试用例往往覆盖率不够,或者在发现故障以后很难构造出与之相应的测试用例。因此迫切需要使在线调试功能能够方便地扩展到一般的处理器上。

针对上述应用需求,这里提出的新调试方法通过引入一种通用的调试模块( Universal Debug Module,UDM) 可以使没有调试接口的处理器建立起标准的调试机制。该调试模块利用处理器的中断机制实现处理器响应断点( breakpoint) 的机制,利用基于双端口RAM 中一种巧妙的地址映射机制实现同时对多行代码设置断点的功能,并且能够方便地实现被调试系统和调试主机之间调试信息和命令的交互。UDM 还具有易于扩展的优点,当SOPC 系统中有多个处理器时可以共用一个UDM。

2 在线调试的一般原理

嵌入式处理器的主流在线调试方法,目前主要有2 种: 后台调试模式( backgroud debug mode,BDM) 技术和基于IEEE P1149. 1 协议的JTAG 调试技术。BDM 技术在Motolora 微控制器中得到了大量的应用,ARM,MIPS 和PowerPC 等处理器都具有基于JTAG 技术的在片调试功能,如ARM 公司提出了基于JTAG 技术的RDI 调试接口标准,主要用于ARM 芯片的调试。处理器内核中通过增加支持调试的扩展设计,可在预留的调试接口输入简单的控制信号,以实现: 处理器挂起( Halt) 、输出PC 值和通用寄存器值、输出和修改Memory 空间中的数据等基本的原始调试操作。通常上述调试接口的设计与指令集架构相关,如MIPS32 提供如下一些调试方法: ①断点指令BREAK; ②一些自陷指令TRAP; ③特殊控制寄存器WATCH,通过编程使得特定的load /store 操作以及取指操作产生特殊的例外;④一种基于TLB 的MMU,通过编程使得访问任意存储器页都可以产生特定的例外。

对于没有调试接口的处理器目前主要是通过在软件和硬件设计中充分考虑可能的调试需求,再加上调试主机和被调试系统之间的通信机制来实现在线调试的。这种调试模式下,调试代码需要插入到正常程序中,将调试信息输出到调试主机,同时还能够接收调试主机发过来的命令做出各种响应。该方法的主要缺陷是针对不同的调试需求,要不断修改正常程序中的调试代码,导致标准化和通用性程度不高。此处的UDM 在不对处理器内核做修改的情况下即可使这类处理器建立起方便的调试机制,是一种不同于主流大型处理器实现在线调试的方法。

3 通用调试模块( UDM) 的工作原理

3. 1 系统描述

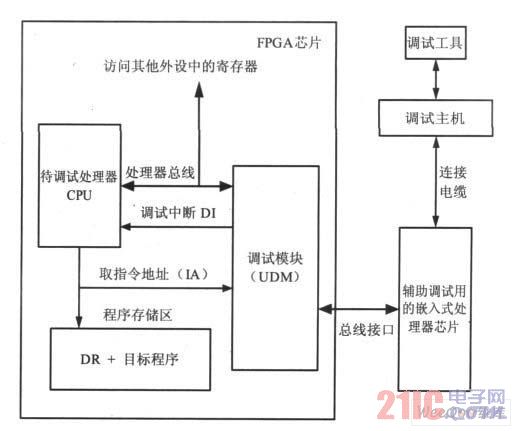

使用UDM 的调试系统框图如图1 所示,利用与FPGA 同在一块PCB 板上的ARM、DSP 等处理器作为辅助调试用的嵌入式处理器( 下文中简称为辅助处理器) ,简化了UDM 与调试主机之间的通信。通过辅助处理器的总线接口,UDM 中的各种控制和数据寄存器被直接映射到辅助处理器的Memory 空间。在辅助处理器开发工具的Memory 窗口直接进行数据读写操作,就可实现对UDM 的操控,如图4、图5 所示。由于在一块PCB 板上同时集成FPGA 和嵌入式处理器芯片是很常见的设计,因此这种通信方式适用的范围很广。

图1 应用UDM 的调试系统框图

UDM 直接作为FPGA 外部辅助调试的嵌入式处理器的外设,如果在外部处理器总线挂接多个UDM 模块,就能实现同时对多个处理器进行调试。

UDM 通过产生调试中断( DeBug Interrupt,DI) 信号,使处理器响应中断并调用调试服务程序( DebugRoutine,DR) 。UDM 通过监测处理器的取指令地址( Instruction Address, IA) 产生DI 信号。PicoBlaze 在运行DR 时可通过其总线接口访问UDM,从而实现调试信息的输出和对调试命令的响应。