ժҪ��Ƕ��ʽ��������SignalTap II��Quartus II�����еڶ���ϵͳ�����Թ��ߣ�������������Ŀ��оƬ�ڲ��źŽڵ㴦����Ϣ�����ֲ�Ӱ��ԭӲ��ϵͳ������������ͨ��һ���ನ���źŷ����������ʵ������ϸ����SignalTap II�Ĺ������̺Ͳ������÷�����ʵ�����������ò��Է����������㣬ʵʱ�Խϸߣ��ܹ��ӿ�ϵͳ�Ŀ������̡�

�ؼ��ʣ�SignalTap II�����ԣ��źŷ�����

����

�������Ӽ�������װ������ӡ�ư����켼���IJ��Ϸ�չ��ӡ�Ƶ�·�����Խ��ԽС���ܶ�Խ��Խ���Ӷ�Խ��Խ�ߣ�����Խ��Խ�ࡣ�ʲ��ô�ͳ��Ӳ�����Է���(����̽����Է�)�����Ժ����ϵ��������Ѷ�����Ƕ��ʽ�������ǵ�ʹ�ÿ��Խ���Ч��Ӳ�������ֶκʹ�ͳ��ϵͳ���Է������ϣ��Ӷ������Щ���⡣Ƕ��ʽ��������ʵ����Ӳ�����Ե�����������������֤����ȷ�Ե�����������������ͬ��������������Ŀ��оƬ�ڲ��źŽڵ㴦����Ϣ�����ֲ�Ӱ��ԭӲ��ϵͳ�������������������š�����������ʹ�ü��۸�͵��ص㡣

1 SignalTap IIԭ������������

SignalTap II����������Quartus II�����еڶ���ϵͳ�����Թ��ߡ�����һ�ֻ����������˵�Ƕ��ʽ�������ǣ������߱���ͨ�������ǵĴ��������ݲɼ��ʹ洢���ܣ����ɷ���FPGA�����ڲ��������źźͽڵ㣬��ϵͳ����й۲�Ӳ���������Ľ������á�SignalTap IIר����Quartus II������������Ƕ��ʽ����������ȣ���֧�ֵ�ͨ������࣬����������ʱ��������ߡ�ĿǰSignalTap II��������֧�ֵ�����ϵ�а�����Cyclone��Cyclone II��Cyclone III��APEXT II��APEX 20KE��APEX20KC��APEX20K��Excalibur��Mercury��Stratix GX��Stratix��Stratix II��Stratix III�ȡ�

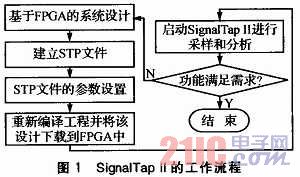

SignalTap II�Ĺ���������ͼ1��ʾ����FPGA���й����У������㴥������ʱSignalTap II�������������̲��������ݴ���Ŀ�������е�Ƕ��ʽRAM(��ESB��M4K)�У��������ݲ���ˢ��Ƭ�ڴ洢�����ݣ�Ȼ��ͨ��������JTAG�˿ڽ������ź����ݴ�������������Quartus II���������н�����ʾ�ͷ��������������߿�����������ƹ�������ϵͳ�����ٶ����۲�Ӳ���������Ľ������á����⣬SignalTap II����������е����в�ε�ģ����źŽڵ���в��ԣ�����ʹ�ö�ʱ�����������һ���ͨ��������ȷ��ǰ�����ź���Ϣ�ı�����

2 STP�ļ��IJ�������

��ͼ1��ʾ��SignalTap II���������У�STP�ļ��IJ��������Ƿ�ǡ����ֱ��Ӱ��������������ĺû��������������������Ǽ�����Ҫ�ġ�STP�ļ��IJ���������Ҫ�������¼������棺

�����ò���ʱ�ӡ�����ʱ�Ӿ�������ʾ�źŲ��εķֱ��ʣ�����Ƶ��Ҫ���ڱ����źŵ����Ƶ�ʣ���������ȷ��ӳ�����źŲ��εı仯��SignalTap II��ʱ�ӵ������ز���������ʹ�����ϵͳ�е��κ��ź���Ϊ����ʱ�ӣ�����Altera��˾�Ľ������ʹ��ͬ��ϵͳȫ��ʱ��

��Ϊ����ʱ�ӡ�������ʵ��Ӧ���У�����ʹ�ö����IJ���ʱ�ӣ������ܲ���������ϵͳ�е������źţ����轫ϵͳʱ�ӽ��з�Ƶ��

�����ñ����źš�������Node Finder���ڽ���ѡ������Ҫ�۲���źš�

�����ò�����ȣ�ȷ��RAM�Ĵ�С��������Ⱦ����˴����źŲ����洢�Ĵ�С�����Ǹ��������ʣ���RAM�������ʹ����źŵĸ��������ġ������źŸ����������Ͳ�����ȵ���dz��ֱ�Ӹı�RAM���ռ�������������ȵķ�ΧΪ0��128 KB��SignalTap II������ʾ�ı����źŲ��ε�ʱ�䳤��ΪTx=N×Ts������NΪ�����д洢�IJ���������TsΪ����ʱ�ӵ����ڡ�

������buffer acquisition mode��buffer acquisitionmode����ѭ�������洢�������洢����ģʽ��ѭ�������洢Ҳ���Ƿֶδ洢������������ֳɶ��Ƭ��(segment)��ÿ��������������ʱ�Ͳ���һ�����ݡ��ù��ܿ���ȥ���ص����ݣ�ʹ���������ʹ�ø�����ͨ��ѡ��ѭ�������洢����Ҫ���ô���λ�á�����λ������ָ����ѡ��ʵ�����ڴ�����֮ǰ�ʹ�����֮��Ӧ�ɼ�����������Pre trigger position��ʾ������������12��Ϊ����ǰ��88��Ϊ������Center trigger position��ʾ���������ݴ��ڴ���ǰ���һ�룻Post trigger position��ʾ������������88��Ϊ����ǰ��12��Ϊ������Continuous triggerposilion��ʾ�Ի��λ���ķ�ʽ���������������棬ֱ���û��ж�Ϊֹ��

�ݴ�������SignalTap II֧�ֶഥ�����Ĵ�����ʽ������֧��10��������Ϊ���ø��ӵĴ��������ṩ���㹻������ԣ�������֤�������������˶ഥ������ֱ�����еĴ�������˳������ſ�ʼ�ɼ����ݡ�

�����������趨Լ���ԵĴ��������������趨�����źŵĶ�������������ֱ�Ӳ��õ����ⲿ�����ģ���ڲ����źţ�Ҳ������������ڵ��źŵ���ϸ��Ӵ����������ɴ��������Ĵ����������̣���Э�����Թ�������������������ʱ����SignalTap IIʱ�ӵ������ز��������źš����磬ʹ���ź�EN��RST���������������=ENA&RST��

������������ú����±��빤�̲�����������ص�FPGA�У���Quartus II��SignalTap II�����²鿴�������Dz���������������ط��������ϵͳ���ԡ�