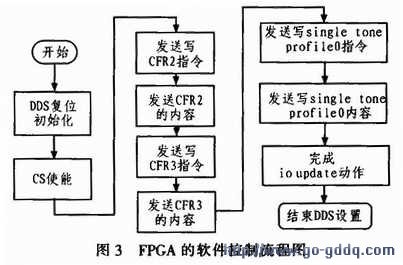

首先,对系统进行初始化,对FPCA的各控制信号进行复位操作,使能CS信号。

其次,对3个主要的寄存器进行设置。设置地址为0X01的寄存器CFR2,共32位,这里只需要使能第24位单音模式profile的幅度值,默认值为0,这里设为1,其余均使用默认值,因此地址为0X01寄存器的内容为0X01_40_08_20。

地址为0X02的寄存器CFR3主要用来设置PLL和VCO的参数。其中,第26位到第24位用来选择PLL VCO参考时钟的频带,这里选择820~1 150 MHz的VC05,因此为101;第8位是PLL使能的选择,默认值为0,这里选择使能1;第7位到第1位这7 bit数据是PLL倍频器的倍频系数,默认值

为0000000b,这里对外部时钟进行40倍频,因此,设置为0101000b。其余各位均使用默认值。所以,地址为0X02寄存器的内容为0X1D_3F_41_ 50。

对地址为0X0E的单音模式profile进行设置,它是用来控制DDS的幅度、相位和频率。其中第61位到第48位这14位用来设置幅度值,根据需要在评估软件中输入所需幅度值可以直接查看寄存器中相应位的值,这里使用默认值00_1000_1011_0101b;第47位到第32位这16位用来设置相位偏移量,这里仍旧使用默认值0X0000;低32位是用来设置频率控制字的值,频率控制字![]() ,其中,fout为输出频率,N为频率控制字的位数,位数越大输出频率的分辨率越高,fc为系统时钟1 GHz,这里输出频率为50 MHz,对应的频率控制字为214748365,因此对应位的值设置为0X0CCC_CCCD。地址为0X0E寄存器的内容为0X0885_0000_0CCC_CCCD。

,其中,fout为输出频率,N为频率控制字的位数,位数越大输出频率的分辨率越高,fc为系统时钟1 GHz,这里输出频率为50 MHz,对应的频率控制字为214748365,因此对应位的值设置为0X0CCC_CCCD。地址为0X0E寄存器的内容为0X0885_0000_0CCC_CCCD。

最后,结束IO_UPDATE的操作动作,完成一次完整的设置过程。

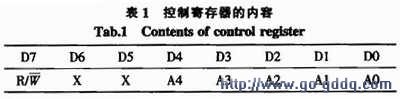

对寄存器的读写操作是通过向输入端口SDIO发送8位指令来实现的,这8位中,最高位为读写指令,1为读操作,0为写操作,低5位用来选择在通信周期时选通哪个寄存器进行数据的传输,控制寄存器的内容,如表1所示。

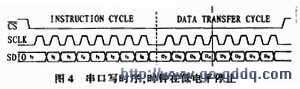

对AD9910读写操作时,需要注意AD9910的时序要求。对于串行I/O端口的各种控制信号之间的有4种基本的时序关系,分别是串口写时序,时钟在低电平停止;三线串口读时序,时钟在低电平停止;串口写时序,时钟在高电平停止;两线串口读时序,时钟在高电平停止。这里采用第一种时序关系,时序图如图4所示。

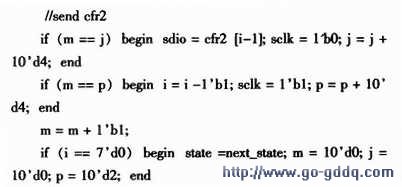

在SCLK上升沿,写入数据有效,FPGA控制SCLK信号的产生。具体写入数据的程序代码(使用Vefilog HDL编写)如下所示:

该指令用于对地址为0X01的控制寄存器CFR2进行写操作。鉴于FPGA的高速处理能力,在程序设计时需要注意一些特殊的时序要求,如以下几个方面。

1)AD9910开始工作时必须先将其复位,复位时间保持1 000个系统工作周期。

2)如果系统工作需要多次使用I/O_UPDATE,要注意I/O_UPDATE引脚置1的时间控制,这关系到系统能否顺利设置各个寄存器。