摘要: 宽带短波信道模拟器是一种运用仿真技术对真实的短波信道进行模拟的仪器。首先指出数字下变频在宽带短波信道模拟器中的作用。然后,阐述了数字下变频中的数控振荡器、CIC 滤波器、半带滤波器和低通滤波器的实现方法。最后,结合Matlab 算法仿真技术,不依赖FPGA 的IP 核,设计并实现了基于FPGA 的数字下变频。功能与时序仿真结果表明: 基于FPGA 设计实现的数字下变频能够满足宽带短波信道模拟器性能指标要求,并且具有灵活性、通用性和修改参数方便等特点。

0 引言

短波通信信道具有时变和色散的特性,并且容易受到噪声干扰,所以模拟其传输特性,具有很高的实用价值。短波信道模拟器借助先进的仿真技术手段实现在实验室环境下进行通信试验,因其具有有效性、经济性、安全性和直观性等特点,在通信试验中可广泛使用。传统的短波信道模拟器大部分停留在话音带宽上,其主要不足是功耗过高、体积庞大、可控性不高及实时性不好。模数转换器( A/ D)器件和数字信号处理理论的飞速发展,为研制宽带短波信道模拟器奠定了坚实的基础,但由于现有的数字信号处理器( DSP) 处理速度有限,往往难以对高速率A/ D 采样得到的数字信号直接进行实时处理,为了解决这一矛盾,需要采用数字下变频( DDC) 技术。所以数字下变频技术在宽带短波信道模拟器的数字化和软件化过程中起到了重要的作用。FPGA 具有较高的处理速度和很强的稳定性,而且设计灵活、易于修改和维护,同时可以根据不同的系统要求,采用不同的结构来完成相应的功能,大大提高系统的适用性及可扩展性。因此,FPGA 逐渐成为实现DDC 的首选。

1 宽带短波信道模拟器设计

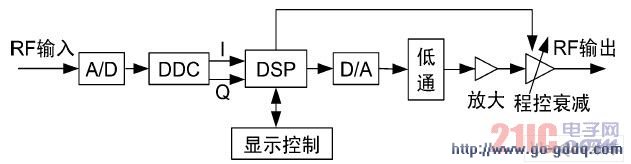

宽带短波信道模拟器的输入为短波调制信号( 3~ 30 MHz) ,首先经过高速A/ D 直接进行采样,将模拟的调制信号转换为数字信号,然后再通过数字下变频技术分离出I、Q 两路数字基带信号,以便于后续的数字信号处理。信号处理中通过显示控制设备对信道参数进行设置和输出。最后处理好的信号再经过D/ A 转换后,通过低通滤波器、放大器和程控衰减等设备输出最终所需的模拟信号。这样就大大降低了ADC 和DSP 器件性能的要求,减轻了数字信号处理的负担,便于实现并有效降低成本。宽带短波信道模拟器的体系结构如图1 所示。

图1 宽带短波信道模拟器的体系结构图

宽带短波信道模拟器通过数字下变频降低采样数据率,减轻后续信号处理的压力。数字下变频在模拟器中起到前端ADC 和后端DSP 器件之间的桥梁作用。在数字下变频部分中可以方便地对接收信号频段和滤波器特性等进行编程控制,极大地提高了宽带短波信道模拟器的性能和灵活性,对于系统的升级或是兼容,都非常方便。

2 基于FPGA 的数字下变频实现方案

宽带短波调制信号的输入频率为3~ 30 MHz,根据带通采样理论,在工程实现上,信号采样速率一般为模拟信号带宽的2. 5 倍左右,考虑到在器件满足要求的前提下可以尽量提高采样频率,选用了64 MHz 作为ADC 的采样频率。经过数字下变频的32 倍变频,最终输出到DSP 的信号带宽为2 MHz。

该文中的DDC 实现不采用ALTEra 公司所提供的IP核,这样可以降低成本,减少对国外技术依赖。

FPGA 器件采用cyclone III 器件,它是Altera 公司新一代采用SRAM 工艺低成本的FPGA,该系列器件的特点是低成本、低功耗和高性能。具有嵌入式乘法器,实现专门的乘法和乘加运算,还可实现有限脉冲响应( FIR) 滤波器; 最多有20 个全局时钟,支持动态时钟管理以降低用户模式时的功耗; 并且有4个锁相环( PLL) 。根据该设计的数据处理要求,估算处理所需的资源,以及引脚封装有利于制板的原则,选用EP3C40Q240C8N 型FPGA,并在开发工具Quartus II 上对信号发生器的设计、综合及仿真。