������ѹ�����������Ӽ�·���������ѹ�� dV/dt ������ �������� ��

������ʱ�����Լ��ͻ���ر�¶��ƽ�������͵�·�IJ������档���ְ����й���Դ��ѹ��·����ƣ���·��һ�ε�Դ����ȫ�����涨������̫�մ��Ĺ����չ⡱��ͷ�����ͬλԪ���ȵ緢����������Ӧ����Ҫ�����ϸ�Ŀ��Ƶ������ģ�����˲��������ĺͺ������ļ�壬������Щ�ϵ�ʱ���ͷ����ġ�����������һ�ε�Դ��ʹ��Ӧ˲��Ĺ������ϣ������������Ե���ѹ�����رա�ͨ�����ֹ�������ѹ�������ȥ������ͷŵĵ����������

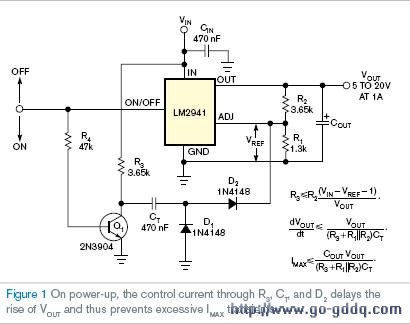

����������ѹ���������������ļ�壬�������ѹ�������ѹ���������벢������ܵ��ݵij˻���ȣ�IMAX=dV/dt��COUT������IMAX����������dV/dtΪ��ѹ��ʱ����֣�COUTΪ������ݡ���ʽ���� ������ѹ�� ��ͨ����������Ѳ���������dV/dt����ͼ1��·�������������ʹ�ù�ҵ���Ŀɵ�������ѹ�����������е�low-dropout LM2941��

��������dV/dt�����Ļ�������6������������R3��R4��CT��D1��D2��Q1���ϵ�ʱ�����Ƶ���ͨ��R3��CT��D2ʹ�����ѹ�����ӳ٣������ֹ�˹����˲ʱ��������

�����������乤�����̡���VIN����Q1�ر�ʱ������ͨ��R3��CT��D2������ѹ���ο��˵��ο���ѹ���������������VOUT ��dV/dt��CTͨ����������ŵ�����ʣ�(R3+R1R2/(R1+R2))��ʹ�ù�ʽR3=(VIN�CVREF�C1)/VOUT��R4=<20R3,��CT=COUTVOUT/(IMAX(R3+R1R2/(R1+R2)))���Ӷ�����IMAX���κ���Ҫֵ�����磬�ٶ���·��ͼ��ʾ��COUT=100 &mICro;F��dV/dt=2500V/s����IMAX=0.25A���ڸĽ����ϵ����к�D1��D2����ѹ�����������з���dV/dt��·����ֹ�����뵽����Ʋ���ѹ����ϡ�

����Ӣ��ԭ�ģ�

����Circuit limits dV/dt and caPACitor inrush at regulator turn-on

����Adding a simple circuit to the adjust PIN of a regulator controls the dV/dt of the output voltage, limiting inrush current.

����W Stephen Woodward, Chapel Hill, NC; Edited by Charles H Small and Fran Granville -- EDN, 10/11/2007

����Unusual design constraints sometimes reveal the unfriendly side of everyday components and circuits. A case in point is the design of power-supply-regulation circuitry in which the primary power source has an absolute current-limit specification, such as spacecraft photovoltaic, or ��solar,�� panels and radioisotope-thermoeleCTRic generators. Such applications require that you pay scrupulous attention to strict control of current consumption, including transient-current consumption, and infrequent consumption spikes, such as those that typically oCCur on power-up. The problem is that current-limited primary-power sources CAN suffer catastrophic voltage droop and shutdown in response to momentary overcurrent faults, even when the fault is brief. Common causes of such faults are the current spikes that charge the regulator output��s decoupling capacitor.