共模抑制比变差将导致 数据采集器 抗共模干扰能力下降,使采集器的测量精度降低。对共模抑制比影响最大的为电阻R8~R11和运算放大器U3构成的共模抑制电路,他对采集器的共模增益和差模增益都有影响。前部PGA电路对共模抑制增益影响很小,可以忽略不计。

图2所示电路R9处可以设置偏置电压,先设定为接地。设定共模抑制电路输入共模电压为VOC,差模电压为Vod,共模抑制电路输出电压的计算公式为:

![]()

由上式可见不同电阻的变化,对于共模输入和差模输入的输出造成的变化是不相同的,对于R8和R9变化时,Aod和Aoc同时变大或同时缩小,对于R10和R11,Aod和Aoc输出向相反方向变化。

在PGA的两个输入端输入同一个电压作为共模电压,采用端点法计算获得各档的共模增益Aoc。用差模增益Aod除以共模增益Aoc得到共模抑制比CMRR。

表2列出了利用电路仿真结果计算得到的增益和共模抑制比。在正常状态下,数据采集器共模抑制比应大于120 dB。

表2两组数据共模抑制比均小于120 dB,因此共模抑制电路故障。第一组数据差模增益和共模增益

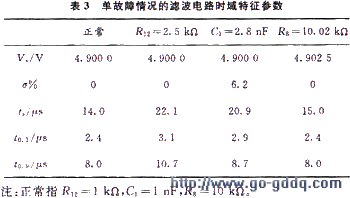

2.4 滤波电路的检测原理

滤波电路故障可能造成数据采集器 模拟电路 建起时间过长、产生过冲等故障,同时会影响采集器的频率特性。由于采集器的时域特性比较重要,而且频率信号不易产生,采用时域法,通过分析其阶跃响应上的时域特征判断滤波电路是否故障,当0.01%电路稳态误差的建起时间ts超过最大允许建起时间时认为电路故障。

本例滤波电路由电阻R12和R13,电容C1和C2以及运算放大器U4组成,他的传递函数为:

![]()

由上式可以得到,滤波电路不影响增益。正常工作状态时,滤波电路处于过阻尼状态。R12,R13,C2阻抗增大将导致阻尼增大,建起时间ts也将增大;C1增大使阻尼减小,严重时将造成电路振荡。上升时间tr越小,愈多高频信号可以通过滤波电路。对于相同电压,当增益越大时,建起时间越长;对于相同增益,输出电压越大,建起时间越长。

前部放大器电阻故障也会影响到阶跃响应的曲线,但对电路的建起时间影响较小,通过分析采集器阶跃响应的建起时间ts和稳态电压Vs可以分辨出是否滤波电路故障。为了可以分辨出增益是否变化,在最大增益下输入略小于最大量程电压的阶跃信号。表3列出了4组10倍增益0.49 V输入的阶跃响应仿真数据。考虑到电路时钟频率,时间测量的分辨率为0.1μs。

根据数据采集器的总体设计要求电路最大建起时间为20μs。第二组和第三组数据的ts值超过最大建起时间,最大建起时间时采样电压Vs明显低于正常值,可以判断为滤波电路故障。第三组数据的超调σ%不为零,而且到达90%稳态值的时间t0.9较短,判断是C1故障引起振荡。第二组数据没有超调,为电阻R12,R13或C2故障,而上升时间较长,显示有更多高频信号被滤掉。第四组数据建起时间正常,但Vs明显大于正常值,判断是放大器可能故障,可以再由放大增益相对误差确认故障。

3 自检测 的实现

3.1 自检测电路的设计

由于BIT技术需要增加额外的电路,为了控制设备的成本,减少新增电路对设备可靠性和电路复杂性的影响,BIT技术应在尽可能少增加附加电路的基础上,检测出尽可能多的故障状态。

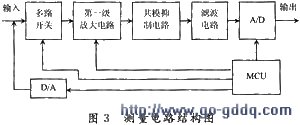

由前述检测原理归纳可得出为满足BIT的要求,主要有两种测试信号需要注入到模拟电路中。一种是直流电压信号,一种是阶跃信号。使用MCU控制一个附加的D/A输出所需的测试信号。电路结构图如图3所示。

3.2 测试信号的注入

用作检测的信号自身也需要具有较高的精度。为控制采集器精度在0.2%,选用的D/A需要具有0.01%的精度。由于偏置电压只用于中间处理,只需要具有良好的漂移特性和0.1%的精度即可。

为了测量数据采集器的差模增益,可在多路开关输入端输入一直流电压,幅值为各档满量程的10%和90%电压,由此获得8个输出电压,并通过端点法计算各自的差模增益。测量共模抑制比时,可在增益为10倍时通过多路开关向PGA输入一个幅度为10 V的共模电压,并测量由共模电压产生的共模误差输出电压,然后根据该电压计算出共模抑制比。

阶跃输入信号用于测量采集器的建起时间,超调量等时域参数,这些参数将作为诊断滤波电路故障的依据。在10倍增益时输入0.5 V的阶跃脉冲,获得阶跃响应全过程的电压输出曲线。为了测量阶跃信号的输出响应,A/D芯片需要较高的采集速率,从而能在上升时间采集尽可能多的数据。当A/D 芯片采集速率较低时,可以采用输入阶跃脉冲群,同时控制A/D芯片采集的时钟周期与脉冲周期相差一定时间△t,依次测量多个阶跃脉冲响应,从而获得阶跃响应曲线。