摘要:在TMS320DM643平台上实现H.264基档次编码器的移植与优化显得格外实用和必要。基于对DSP平台的结构特性和H.264的计算复杂度分析,主要从核心算法、数据传输和存储器/Cache使用几方面对H.264编码器进行了优化。实验结果表明,对于CIF格式的视频序列,优化后的H.264编码器能够达到每秒高于24帧的编码速度,满足了视频处理对于实时性的要求。

关键词:H.264编码;TMS320DM643;算法优化

0 引言

针对视频通信中传输带宽或存储容量与视频质量的矛盾,ITU-T的VCEG和ISO/IEC的MPEG联合制定了低码率视频压缩标准H.264。相对于以往的标准,H.264除了增强了网络适应能力外,大幅度提高了压缩编码效率,在相同的码率下能够获得更高的主客观质量。2003年5月,H.264/AVC标准正式推出,正式名称为H.264 MPEG-4 part 10 AVC(Advanced Video Coding),以下简称为H.264标准。

1 编码器

H.264仍采用图像预测和变换编码相结合的编码结构,编码器采用的仍是变换和预测的混合编码法。输入的帧或场以宏块为单位被编码器处理。首先,按帧内或帧间预测编码的方法进行处理。如果采用帧内预测编码,其预测值PRED是由当前片中前面己编码的参考图像经运动补偿(MC)后得出,与解码所需的一些边信息(如预测模式量化参数、运动矢量等)一起组成一个压缩后的码流,经NAL(网络自适应层)供传输和存储用。为了提供进一步预测用的参考图像,编码器必须有重建图像的功能。因此必须使残差图像经反量化、反变换后得到。为了去除编码解码环路中产生的噪声,为了提高参考帧的图像质量,从而提高压缩图像性能,设置了一个环路滤波器。即重建图像可用作参考图像。

1.1 视频编码的硬件结构

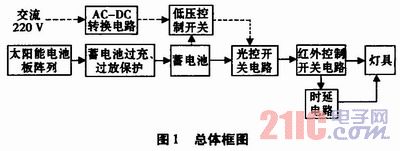

H.264视频编码器硬件结构如图1所示。FLASH模块用于存放程序,EEPROM用于存放编码系统的初始化配置信息和系统MAC层地址。片内SRAM用于缓存当前正在处理的宏块数据,以及一些频繁调用的数据段和程序段。外接存储器SDRAM主要用于存储原始帧、参考帧和重建帧的源数据。片内、片外存储器之间的数据传输借助EDMA在后台操作,这样可并行处理数据传输和运算操作,提高效率。

1.2 DSP芯片简介

DM643的EDMA可在64个独立的通路上,提供超过2GB/s的I/O带宽。此外,运用两级片内高速缓存Cache和64位外部存储器接口(EMIF),可方便地实现与同步/异步存储器的无缝连接。DM643还集成了多种新型的片内外设,以适应于媒体数字化处理和网络通信的应用:(1)三个可配置的视频端口,提供和通用视频A/D和D/A芯片的无缝接口;(2)压控晶体振荡器插值控制端口,用于与MPEG-2传输流接口时的系统时钟恢复;(3)管理数据输入输出模块,用于列举系统中的物理层设备并监视它们的连接状态。