1.6 CPLD模块

CPLD采用ALTEra公司的MAXⅡ系列的EPM2210F324来实现系统电源上电顺序控制电压监测、软件看门狗、时钟综合器的配置和FPGA与DSP的程序加载等功能。具体实现如下:系统上电时根据系统电源上电要求,控制电源模块加电使能端来控制上电顺序。通过电压监测芯片,对系统电压异常进行监测,根据异常情况进行系统复位或切断电源。通过内建计数器,实现软件看门狗功能,软件看门狗可以通过DSP使能打开或关闭,以方便系统调试。系统正常上电后通过SPI配置时钟综合器,产生系统所需的时钟。时钟配置完成后,CPLD控制FPGA采用FPP方式从FL-ASH中加载程序,当FPGA加载成功后,根据FPGA的配置引脚CONFIGDONE状态,将FLASH控制权交给DSP,控制DSP完成程序的加载。

1.7 时钟和电源模块

实现数字中频调制解调系统的时钟电路设计如下:板内40 MHz恒温晶振与外部供给的10 MHz原子钟通过时钟综合器ADI公司的AD9522做双时钟切换、主备时钟备份,CPLD根据需要配置时钟综合器生成DSP与FPGA的40 MHz工作时钟、AD9233的40MHz或80 MHz采样时钟、AD9957的800 MHz输入时钟。电源采用凌特公司的LTM4600产生FPGA和DSP的I/O电压3.3 V和FPGA的核电压1.1 V,采用凌特公司的LT1764产生FPGA的2.5V电压,采用TI公司的TPS54310产生DSP的核电压1.2V,用凌特公司的LT1764产生AD9233的模拟电源1.8V和AD9957的模拟电压3.3V。

2 软件设计

2.1 MSK数字扩频调制

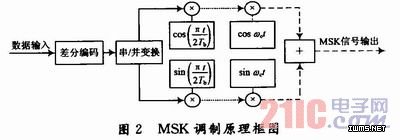

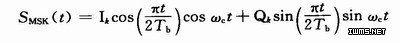

根据理论分析,MSK可以看作是具有正弦加权的OQPSK,系统采用具有正弦加权的OQPSK的调制方案,原理框图如图2所示。

在硬件电路实现时,MSK基带调制(图中实线部分)在FPGA中实现,当接收到系统的发送允许St_TCLK时,启动MSK基带调制,从RAM中读取发送信息数据,从低位开始进行差分编码、根据消息和伪码进行伪随机扩频,将扩频后的数据进行串并变换、正余弦加权运算,之后将正余弦加权后数据送给D/A处理。中频调制(图中虚线部分)采用AD公司的带D/A转换的正交数字上变频器AD9957完成,AD9957可以实现数据的内插滤波、正交上变频、D/A转换输出等功能,本系统设置中频频率为70 MHz。

由于基带MSK调制就是对并行的两路数据进行正弦加权,即每个比特对应于周期为fb/4的半个的正弦波形,根据0/1选择不同的相位,因此在具体实现中,可以采用查找表的方法,根据内插系数先产生半个波长的正弦波信号数据进行存储,在调制时根据数据选择输出不同相位的半个周期正弦波形。

上一页 [1] [2] [3] [4] 下一页