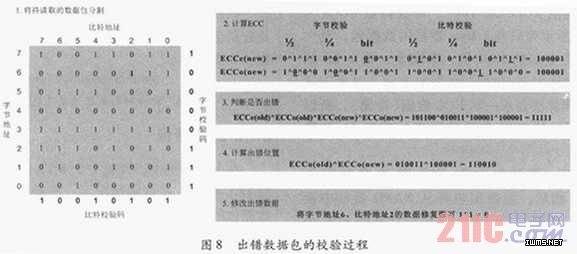

当数据包发生错误时,错误检测和更正所使用的方法与先前所描述的方法相似,这里仍以1 bit错误来说明校验过程,具体如图8所示。

经步骤1~步骤4的计算,新的数据包存在错误且出错位置为“110010”,由于前面将字节校验码设为ECC值的高位,比特校验码设为低位,因此,“110010”的高有效位表示出错的字节地址,低有效位代表出错的比特地址,即字节地址为6、比特地址为2的数据发生了错误,与设定的错误情况相符。此时,只需将该位的数据比特与“1”异或即可完成数据包的修正。

将8 Byte数据包扩展到512 Byte数据包,虽然数据量大大增加,但仅添加了数据分割的情况,算法仍然一样。计算所得奇偶ECC数据均为12 bit长,其中,3个低有效位代表bit地址(7~0),9个高有效位代表512Byte的地址(255~0)。

3 实验分析

本实验处理对像为256 Byte的数据包,对其进行ECC校验共生成22 bit校验数据。为方便读取,可以在末尾添加两位,形成完整的3Byte校验数据。这3 Byte共24 bit,分成两部分:6 bit的比特校验和16 bit的字节校验,多余的两个比特置1并置于校验码的最低位,在进行异或操作时此两比特忽略。

当往NAND Flash页中写人数据时,每256 bit生成一个ECC校验,称之为原ECC校验和,并保存到页的OOB数据区中;当从NAND Flash中读取数据的时,每256 bit又生成一个新ECC校验,称之为新的ECC校验和。校验时,将从OOB区中读出的原ECC校验和与新ECC校验和并执行按位异或操作,若计算结果为全“0”,则表示不存在出错,并将出错状态变量errSTATUS赋值为“00”;若结果为全“1”,表示出现1个比特错误,将errSTATUS赋值为"01”并进行纠正;除全“0”和全“1”外的其他情况将errSTATUS赋值为“10”表示出现了无法纠正的2 bit错误,如表1所示。

实验仿真环境为ALTEra Quartus II 7.0,编程语言为VHDL。VHDL语言为硬件编程语言,具有并行处理的特点,而原程序中有大量的需要并行处理的异或操作,因此程序执行效率高,非常有利于硬件实现。