3 系统软件设计与仿真

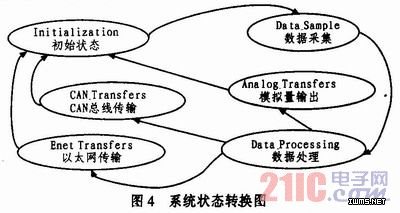

该系统以XILINX公司的XC3S4005PQ208C作为中央处理器,整个系统主要包括初始状态(Initialization)、数据采集状态(Data_Sample)、数据处理状态(Data_Processing)、以太网传输状态(Enet_Transfers)、CAN总线传输状态(CAN_Transfers)、和模拟输出状态(Analog_ Transfers)等6种状态,因此,可以利用有限状态机的设计方案来实现。其状态转换图如图4所示,通过开发工具ISE10.1对各个模块的VHDL源程序及顶层电路进行编译、逻辑综合,电路的纠错、验证、自动布局布线及仿真等各种测试,最终将设计编译的数据下载到芯片中即可。

初始状态:实现系统初始化;数据采集状态:完成数据采集过程;数据处理状态:对采集的信号进行一系列的滤波处理,非线性校正等;以太网传输状态,CAN总线传输状态:根据实际需要将信号数字输出;模拟输出状态:进行数模转换,输出标准的电压电流信号。

3.1 数据采集的FPGA设计

数据采集是工业测量和控制系统中的重要部分,它是测控现场的模拟信号源与上位机之间的接口,其任务是采集现场连续变化的被测信号。对数字系统来说,数据采集主要由传感器放大电路和A/D转换电路构成,由硬件电路可见,系统通过AD7264模/数转换器来实现模/数转换。AD7264内含6个寄存器,分别是A/D转换器的结果寄存器、控制寄存器、A/D转换器A和B的内部失调寄存器、A/D转换器A和B通道的外部增益寄存器。由于XC3S4005PQ208C和AD7264都兼容SPI接口,两者的编程只需按照时序图进行即可。AD7264与FPGA的接口主要包括PD0数据输入选择端:DoutA(DoutB)两路数据输出端;OUTa(OUTb)两路数据输入端;CoutA(CoutB、CoutC、CoutD)比较器输出;G3(G2、G1、G0)四路增益控制输入信号。增益由控制寄存器的低四位控制;ADSCLK时钟信号;ADCS片选信号,低电平有效。AD7264工作频率为20 MHz,在CS下降沿,跟踪保持器处于保持模式。此时,采样、转换同时被初始化模拟输入。这需要至少19个SCLK周期。第19个SCLK的下降沿到来时。AD7262恢复至跟踪模式,并设置DOUTA、DOUTB为使能。数据流由14位组成,MSB在前。图5为AD7264读寄存器时序仿真图。