1 �� ��

�����״����̽��ͳ��������ϵͳ��Ϊ����߶�Ŀ��仯ʵʱ���ٺͲ������ͱ��뾡�������źŴ�����ʱ�䣬���������㴦��ʱ����ˮ��Ŀ���̽�����ܲ����ϴ��Ӱ�졣���ɵļ�������ͻ�Ѹ���½���������ȫʧȥ���������������Ӧ�����γɼ���(ABF)���������ܹ�������Χ�����������ı仯�����ϵ��Զ����ڱ����IJ�������Ӧ��Χ���������Ƹ��Ų���������źš���˲���FPGA��ʵ������Ӧ�����γ��㷨�����㸴�Ӻ����������в����γɵĽϺ�;����

������С��������Ӧ�㷨(Least Mean Square��LMS)����������Ӧ�㷨���нṹ��������С������ʵ�ֵ��ص㡣FPGAʵ��LMS����Ӧ�����γ��㷨�Ȳ�������DSP��ʵ�ֿ�����������źŵĴ����ٶȣ���Լ��Դ���ܸ��õ����㸴�Ӷ��ĺ��������й㷺��ʵ�ü�ֵ��

���������γ�ϵͳ�൱��һ��ʱ���˲���������Ӧ�����γ�ϵͳ�ɲ���IIR��FIR���ֽṹ����IIR�˲�����ȣ�FIR�˲������������ŵ㣺�ɵõ��ϸ��������λ;��Ҫ���÷ǵݹ�ṹ�����������Լ���ʵ�ʵ������������У������ȶ���;���ڳ弤��Ӧ�������ȵģ���˿����ÿ��ٸ���Ҷ�任�㷨�������ٶȿ�;FIR�˲�����Ʒ�����

�������IJ�������Ӧ��FIR�˲����ṹ�����ʱ����С����(DLMS)�㷨���������FPGAоƬ�����ٶȿ죬�洢��Դ�ḻ���ŵ���ƺ�ʵ���˻���FIR������������Ӧ�����γɡ����������ź�Ϊխ���źţ�ͨ�����ø�����ʽ��ʾ���ڿռ��˲���ģ�������ѭ����λ��ˮ�˼�����ʹ�����˼������Լ�˴�����Դ��ͬʱ�ò��г˷��������DLMS�㷨����������ϵͳ����Ӳ��ģ��ͷ��������

����2 �������в����γ�ϵͳģ�ͼ�ԭ��

����2.1 ϵͳ�ܹ���ԭ��

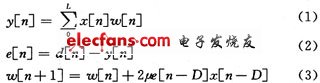

��������Ӧ�����γ��ֳ�����Ӧ�����˲�������ͨ���Ը���Ԫ��Ȩ���п����˲������ﵽ��ǿ�����źš����Ƹ��ŵ�Ŀ�ģ����������Ը����źŻ����ı仯�����ı����Ԫ�ļ�Ȩ���ӡ�������������£�����Ӧ�����γɼ���������Ч�����Ƹ��Ŷ���������(����)�źţ��Ӷ�ʹ���е�����źŸ���������(SINR)�ﵽ�������Ӧ���̵�ʵ�ֿ��Բ����κ�һ�������ں���ṹ�˲���������Ӧ�����㷨������Wiener�˲�����������С����(LMS)�㷨������Ʋ�����С����(LMS)�㷨��ϵͳ�ṹԭ����ͼ1��ʾ��

��������FIR����Ӧ�����γ�ϵͳ�������£�һ���棬�����ź����ʾ��nʱ�̵�ֵ�ɵ���Ȩϵ��ω1(n)��ω2(n)��…��ωm(n)��˺���ӵõ����;��һ���棬������ź��������źŽ��жԱȣ����õ����ֵͨ��һ����DLMS����Ӧ�����㷨����������Ȩֵ���Ա�֤�ռ��˲����������״̬��ʵ���˲���Ŀ�ġ�

����FIR������ϵͳ���ۿ�֪����ij���ʶ������£����뵽����ϵͳ��һ�������ȫ���Ա���ϵͳ�������Ǵ���������ɢ����ʱ������ϵͳ����Ӧ(�����Գ������Ӧ)Ҳ�����ġ�������ϵͳ����һ���ռ��˲�������ͨ���ع۲����Գ������Ӧ�����ǾͿ�����ȫȷ�����˲�����ͨ�����ַ�ʽȷ�����˲�����Ϊ�������Ӧ(FIR)�˲�����

����FIR�˲������������źŴ���(DSP)�о���ʹ�õ����ֻ������˲���֮һ����һ��ΪIIR�˲�����IIR�˲��������弤��Ӧ�˲�����

��������ʱLMS�㷨(the Delayed LMS Algoritms��DLMS)�У���ϵ�������ӳټ����������ڣ�ֻҪ�ӳ�С��ϵͳ������Ҳ�����˲������ȣ�������ݶȨ�[n]=e[n]x[n]��Ҳ���Ǩ�[n]≈��[n-D]����������FPGAʵ�ֵij˷�����ϵ��������Ҫ�������ˮ�����������һ���ӳ�����D��μΪ�������ӣ�LMS�㷨�ͱ�ɣ�

����2.2 ϵͳFPGA����ģ�����

����FPGA(Field-Programmable Gate Array)�����ֳ��ɱ�������У�������PAL��GAL��CPLD�ȿɱ�������Ļ����Ͻ�һ����չ�IJ��������Ϊר�ü��ɵ�·(ASIC)�����е�һ�ְ붨�Ƶ�·�����ֵģ��Ƚ���˶��Ƶ�·�IJ��㣬�ֿ˷���ԭ�пɱ�������ŵ�·������ȱ�㡣

����Ŀǰ��Ӳ����������(Verilog �� VHDL)����ɵĵ�·��ƣ����Ծ������ۺ��벼�֣����ٵ���¼�� FPGA �Ͻ��в��ԣ����ִ� IC �����֤�ļ�����������Щ�ɱ༭Ԫ�����Ա�����ʵ��һЩ���������ŵ�·(����AND��OR��XOR��NOT)���߸�����һЩ����Ϲ��ܱ������������ѧ����ʽ���ڴ������FPGA���棬��Щ�ɱ༭��Ԫ����Ҳ��������Ԫ�����紥����(Flip-flop)�����������������ļ���顣

����ϵͳ���ʦ���Ը�����Ҫͨ���ɱ༭�����Ӱ�FPGA�ڲ������������������ͺ���һ����·����屻������һ��оƬ�һ��������ij�ƷFPGA����������ӿ���������߶��ı䣬����FPGA�����������Ҫ�������ܡ�

����FPGAһ����˵��ASIC(ר�ü���оƬ)���ٶ�Ҫ��������ɸ��ӵ���ƣ��������ĸ���ĵ��ܡ���������Ҳ�кܶ���ŵ������Կ��ٳ�Ʒ�����Ա��������������еĴ�������˵���ۡ�����Ҳ���ܻ��ṩ���˵ĵ��DZ༭�������FPGA����Ϊ��ЩоƬ�бȽϲ�Ŀɱ༭������������Щ��ƵĿ���������ͨ��FPGA����ɵģ�Ȼ�����ת�Ƶ�һ��������ASIC��оƬ�ϡ�����һ�ַ�������CPLD(���ӿɱ����������)��

����������������Ӧ�����γɵ�ԭ������ѧģ�ͣ�������ƵĻ���FPGA���ֲ����γ�ϵͳ�ṹ��ͼ2��ʾ��8·�����ź�x(n)����ǰ���źŴ�����A/Dת�������ܿ�ģ��Ŀ����½����������ݴ洢ģ��˫��RAM������Ӧ�����γɵľ���ʵ�ֲ������£�

������һ������ʽ(1)�ã�ʵ�������x(n)�͵������Ȩֵw(n)���������֮���ۼӵõ����y(n);

�����ڶ�������ʽ(2)�ã�ʵ�������y(n)������d(n)����õ��������e(n);

��������������ʽ(3)�ã���ʱ��ĵ������P(n)��������2����ˣ��ٺ���ʱ������x(n-D)��˵õ��Ļ�����ʱ��Ȩֵ��ӣ��õ��µ�Ȩֵ������

�������IJ����µ�Ȩֵ���������µ���������ѭ�����е�һ��������ʵ������Ӧ��

�����ɴˣ����ǿ��Խ�ϵͳ��Ϊ���ģ�飺����ģ�飺��Ҫ����ʱ���źţ�����ģ���ṩʱ���źŴ�����ģ��������ͳ�ʼ��;˫�ڴ洢ģ��(�����������ݴ洢ģ�顢Ȩֵ�洢ģ�顢����źŴ洢ģ���)���洢������ģ����������ݺͲ���;����ӦȨֵ����ģ�飬������ģ�飺������ģ����Ժ���һ������ϵ�����µİ���Ӧ�㷨;�ռ��˲����˼�ģ�飺����˲����㣬�õ���������