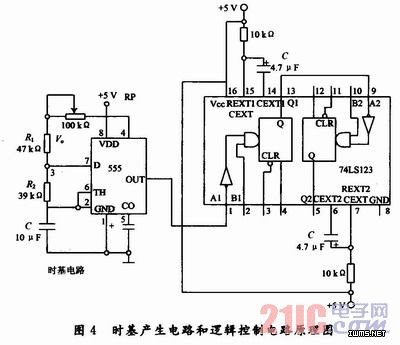

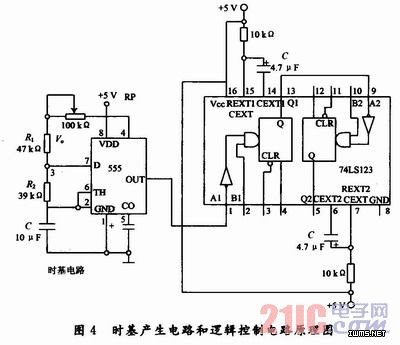

2.2 时基产生电路设计

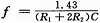

为了获得较为稳定的时间基准信号,以便准确地控制闸门的开启与关闭时间,本设计采取用555定时器组成的多谐振荡器作为时基产生电路,要求其产生频率为1 kHz的脉冲。振荡器的频率计算公式为:

,因此,可确定各个参数,并通过电路仿真得到了比较稳定的脉冲信号,这里取R1=47 kΩ,R2=39 kΩ,C=10μF。为了提高测频精度以及显示稳定,这里加入了一个电位器,可改变振荡器的输出频率,以改变闸门时间。

2.3 逻辑控制电路设计

逻辑控制电路是本设计最为关键和难搞的模块,主要是控制闸门的开启和关闭,同时也控制整机系统的逻辑关系,包括产生74LS90的清零信号,74LS373的锁存信号以及译码显示电路的控制信号。这里采用两个单稳态触发器74LS123组成逻辑控制电路,当

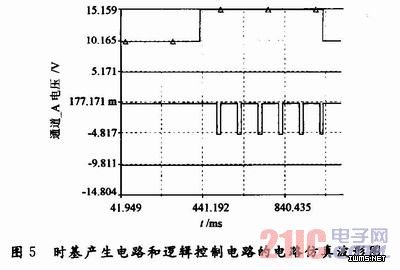

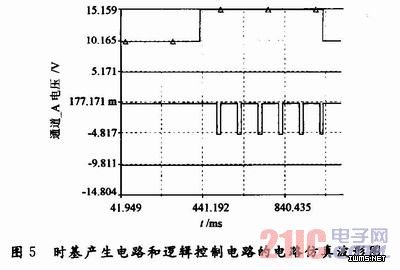

1,触发脉冲从A端输入,其输出信号控制整机系统正常工作。当控制电路输出为高电平时,闸门开启,被测信号通过闸门进入计数电路,于是计数器译码器同时工作,从而记下所测信号频率值。当控制电路输出为低电平时,闸门关闭,计数器停止工作,数码管继续显示所测频率值。直到下一次测量,当手动复位开关S按下时,计数器清零,数码管显示消失,频率计数器完成一次测量。这里闸门采用74LS00与非门。时基产生电路原理图和仿真波形图如图4、图5所示。

上一页 [1] [2] [3] [4] 下一页