・上一文章:录音电子门铃电路

・下一文章:基于GPRS传输的输电线路红外测温系统

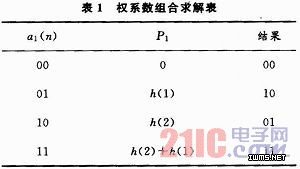

对于a(n)的高位组合,单位积P2可以建立同样的组合表。将P1和P2移位相加,即可得到滤波器的输出结果。在此例中采用的是2位二进制的权系数和输入样本,对于高精度的权系数和输入样本,只不过是增加更多的单位积P3,P4,…等等。

实际操作过程中,基于FPGA的FIR滤波器通过三步完成,第一步将输入信号x(n)进行移位延迟,形成n阶抽头,再将相互对称的抽头相加得到滤波器抽头;第二步在FPGA中构造ROM,按前一步产生的滤波器抽头进行查表运算;最后将所有位的查表运算结果移位相加得到滤波器输出y(n)。

3 试验结果分析

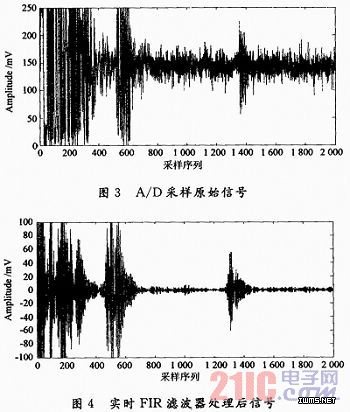

采用ALTEra公司的FPGA器件EPF10K30实现10阶的带通FIR滤波器进行试验。A/D采样频率为40 MHz,精度为12位,声波中心频率为5M-Hz。A/D采样得到的原始声波信号如图3所示。经过FIR滤波器处理后的声波信号如图4所示。

试验结果表明,采用FPGA实现的FIR滤波器有效地消弱了噪声干扰,在保证实时性的基础上,为后期处理提供了可靠的数据。

4 结论

针对超声波信号中的噪声采用基于FPGA的FIR滤波,提高了硬件电路的集成度,并取得了良好的消噪效果。在硬件实现过程中采用查表方法替代滤波过程中的乘法运算,节省了占用的片内资源,提高了处理速度。同时由于采用了并行硬件算法,其处理速度远高于CPU或DSP上的程序处理速度。