・上一文章:GSM手机功率放大器工作原理

・下一文章:GSM手机发射上变频器工作原理

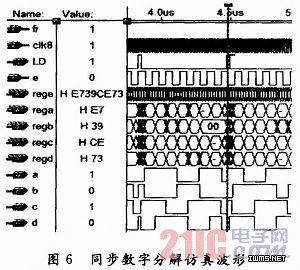

3.4 分解端功能仿真结果分析

与复接端相反,利用CLKS高频时钟读取串行e的码元信号到锁存器rege中,LD信号为内部逻辑产生的控制信号,负责码元分解搬移。由于一帧信号容量过大,故截取了某帧内的一个时隙以便于观察分解还原功能的实现,在32个CLK8时钟周期内从串行输入数据e采集到的码

元信号锁存在rege移位寄存器中,如图6所示,rege=11100111001110011100111001110011B(E739CE73H),从波形图上可见分解后的支路锁存实时状态值为:rega=111001 11B(E7H);regb=OO11l001B(39H);regc=11001110B(CEH);regd=01110011B(73H),而恢复出4个支路的时隙码元信号为:a:11100111;b:00111001;c:11001110;d:01110011。分解过程及其信号分解还原波形如图6所示。

4 结语

本文主要依据PCM30/32基群信号的特点,结合FPGA建模仿真,利用QuartusⅡ8.0仿真综合软件,实现4路低速信号的同步时分复用,提高信号传输效率;并在分解端将其分解还原为4路原始信号。功能仿真结果正确,在允许的信号延时下实现了系统主要功能。系统基于FPGA的设计,便于功能修改和扩展,只需实时修改内部参数即可。