由于网格图的蝶形结构,可以比较PMi-PMj和BMq-BMp(即如果PMi+BMp>PMj+BMq,可以将其写为PMi-PMj>BMq-BMp),这样对于每一对相关状态可以重复使用这两项,在这个过程中需要用到32个加法器。通过这种方法,可以明显减少ACS模块中的加法器数量。

更新路径度量的操作设计如下,编码器的状态转移过程如图2中蝶形结构所示,蝶形结构中两个相关状态转移到两个新状态。

两个相关状态对应的用状态索引分别为i=OD5D4D3D2D1和j=1D5D4D3D2D1,两个新状态可以分别表示为m=D5D4D3D2D10和n=D5D4D3D2D11。即,状态i=0D5D4D3D2D1,如果输入比特0,转移到状态m=D5D4D3D2D10,如果输入是比特1,转移到状态n=D5D4D3D2D11;状态j=1D5D4D3D2 D1,如果输入比特0,转移到状态m=D5D4D3D2D10,如果输入比特1,转移到状态n=D5D4D3D2D11。根据上面的转移状态关系,更新状态的路径度量。

对于幸存分支的存储表示,本文采取如下方法,状态m=D5D4D3D2D10,如果由状态i=0D5D4D3D2D1转移而来,那么此幸存分支取状态的最高有效比特0;如果由状态j=1D5D4D3D2D1转移而来,此幸存分支取状态的最高有效比特1。同样,状态n=D5D4D3D2D11,如果由状态i=0D5D4D3 D2D1转移而来,此幸存分支用0表示;如果是由状态j=1D5D4D3D2D1转移而来,此幸存分支用1表示。每个时刻,经过ACS选出64个状态所对应的幸存分支,存入回溯存储器。

3.3 BM模块

回溯算法,由于已经将每个时钟下所有状态的幸存分支存储在回溯存储器里,在达到译码深度DD后,开始对整个幸存分支进行回溯,如图3所示。当达到回溯深度(Trace Back Depth)后,幸存路径就开始合并,就开始输出译码数据。

回溯指针是卷积码编码逆过程的状态索引。回溯指针的具体建立过程如下:回溯开始时,由ACS中计算的最小度量状态的状态索引作为初始回溯指针,从回溯存储器中读出的所有64个状态的幸存分支中,选出该回溯指针对应的幸存分支,形成下一个回溯指针,以此在回溯过程中循环向前,在每一时钟中形成回溯指针。

由幸存分支的存储表示可以得出,回溯指针m=D5D4D3D2D10,如果该指针对应的幸存分支为比特0,那么下一个回溯指针为i=0D5D4D3D2 D1,如果对应的幸存分支为比特1,那么下一个回溯指针为j=1D5D4D3D2D1;同理,回溯指针n=D5D4D3D2D11,如果幸存分支为比特0,下一个回溯指针为i=0D5D4D3D2D1,如果幸存分支为比特1,那么下一个回溯指针为j=1D5D4D3DzD1。

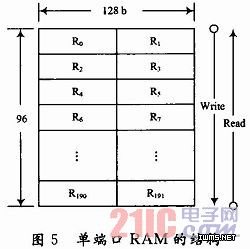

在该设计中,最重要的是译码深度(DD)的选择,译码深度能够决定所用的回溯存储器得深度。结合数据前缀的固定延迟操作,采用一个单端口RAM(SPRAM),大小为96×128 b,如图5所示。

在一个译码周期里,数据前缀译码结束,从数据段(即图3所示start state)开始,每2个时钟往SPRAM里写1次这两个时钟分别产生的幸存分支,共128 b,如图5所示,即顺序写入数据R0R1,R2R3,R4R5,……,往SPRAM里写数据共需192个时钟。在达到译码深度后,开始回溯,读出SPRAM里幸存分支,每个时钟读出两个连续幸存分支,进行回溯指针的操作,在回溯深度后就会合并为一条幸存路径,直到回溯完成,共需96个时钟。在回溯的同时,如有数据输入译码器,开始下一个周期的译码,在回溯操作从SPRAM读数据的96个时钟里,用来译码数据前缀,在数据段开始时往SPRAM里写数据,同时回溯操作的读数据也已完毕。

从SPRAM里读出的数据R(DL+5)~R6(DL为数据长度)中的幸存路径,即为译码比特,输出到输出缓存中。根据系统需要,译码比特输出到输出缓存完成后,一次将最终的译码数据输出。

4 FPGA验证

该设计采用Verilog HDL语言编写代码,使用Quartus 9.0综合,并在ALTEra公司的StratixⅢEP3SL340F151713型号的FPGA上验证,该设计的译码器能达到135.78 MHz的速度,使用FPGA资源为4 992个ALUTs。

5 结语

本文设计的译码器,利用Tail-biting卷积码的循环特性,采用固定延迟的算法与维特比算法结合,使其硬件实现更简单,采用并行结构以及简单的回溯存储器方法,显著提高译码器速度。在设计各个子模块时,优化了硬件结构,减少占用资源和降低功耗,使其整体性能更优。

本文设计的译码器在FPGA上实现和验证,能达到135.78 MHz时钟,该译码器达到了LTE系统所要求的122.88 MHz时钟要求,达到了LTE系统所要求的整体性能,并已应用到ASIC芯片设计中。

上一页 [1] [2] [3]