摘要:基于长期演进(LTE)的Tail-biting卷积码,介绍了维特比译码算法,它是一种最优的卷积码译码算法。由于Tail-biting卷积码的循环特性,采用固定延迟译码的方法,降低了译码复杂度。通过使用全并行的结构及简单的回溯存储方法,设计了一个具有高速和低复杂度的固定延迟译码器。在FPGA上实现并验证,验证结果表明译码器的性能满足了LTE系统的要求。

关键词:LTE;Tail-biting卷积码;维特比译码算法;固定延迟译码;FPGA

引言

LTE(Long Term Evolution)是“准4G”的技术,以OFDM/FDMA和MIMO为其核心技术。它对实时业务、高可靠性业务和广播级多播业务都能提供较好的支持。LTE在20 MHz频谱带宽下能够提供下行100 Mb/s和上行50 Mb/s的峰值速率,高速率对信道编码和译码技术提出了更高的要求。

对于LTE低时延、高速率和高可靠性的要求,降低译码的实现复杂度和时延以及提高其可靠性对LTE系统性能就显得极其重要,也是一个巨大的挑战。

1 LTE中Tail-biting卷积码

卷积码通常用(n,k,N)表示。其中k表示输入编码器的数据位数;n表示编码器输出的数据位数;N为编码约束长度,R=k/n是卷积码的码率。

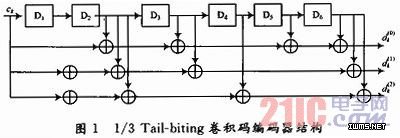

LTE中使用的Tail-biting卷积码编码器结构如图1所示。其约束长度N=7,码率R=1/3。

编码器移位寄存器的初始状态值被设置为相应的输入数据流的最后6个信息比特,以至于移位寄存器的初始状态和结束状态相同。

图1中,D6D5D4D3D2D1表示编码器的状态索引(State Index);ck表示输入数据比特;![]() 表示输出数据比特。

表示输出数据比特。

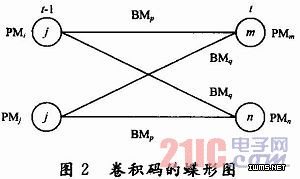

卷积码网格图中的蝶形结构,如图2所示。

随着编码比特的输入,编码器状态的转移过程,由图2可以看出,时刻t-1的两个相关状态Si和Sj转移到时刻t的两个状态Sm和Sn。图中,PM和BM分别表示路径度量和分支度量,其中BM的下标为输出比特![]() 的组合。

的组合。

2 Tail-biting卷积码的译码算法

维特比算法的实质是最大似然译码,它是在卷积码的网格图中寻找一条与编码路径最接近的最大似然路径作为其最终译码输出。在译码的每个时间单元,把网格图上各个分支的度量加到前面状态的路径度量上,比较进入每个状态的所有分支的度量,选择具有最大度量的分支,即幸存路径,迭代上述步骤,最终输出最大似然路径作为其译码输出。

维特比算法主要由三部分组成:分支度量(Branch MetrIC,BM)模块、加比选(Add Compare Select,ACS)模块和回溯(Trace Back,TB)模块。

直接运用维特比算法对Tail-biting卷积码进行译码,其译码复杂度大,不利于硬件实现。为了能降低译码复杂度,用固定延时译码(Fixed Delay Decoding)算法,它是利用Tail-biting卷积码的循环特性,也就是编码输入的开始部分能用来估计译码网格图的最后状态,执行译码操作用的固定延时。

如有一段长为L的软判决数据,选择原数据的后LH个软判决比特,将其放置在数据头部,选择原数据的前LT个软判决比特,将其放置在数据尾部,最后形成长为LH+N+LT的待译码软判决数据。将它用Viterbi算法译码,在译码数据中丢弃前LH个比特和后LT个比特,即为所需译码数据。其中LH和LT分别称为头译码长度(Head Decoding Length)和尾译码长度(Tail Decoding Length),为此算法中需要决定这两个重要参数。