・上一文章:最新全能数控电源IC-ADP1043A(二)

・下一文章:基于LJDZN8400T的智能触摸液晶显示终端控制系统

3 基于FPGA显示屏控制器的设计

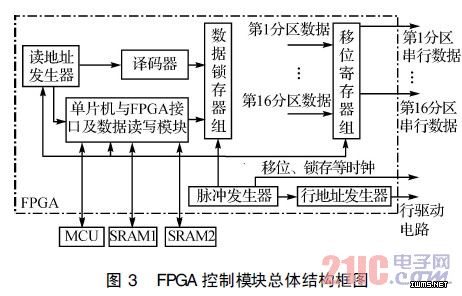

3.1 FPGA控制模块总体方案

如图3所示,FPGA控制模块主要由单片机与FPGA接口及数据读写模块、读地址发生器、译码器、行地址发生器、数据锁存器组、移位寄存器组、脉冲发生器等模块组成。

读地址发生器主要产生读地址信号,地址信号送往MCU接口及数据读写模块,读取外部SRAM1或SRAM2中已处理好的LED显示屏数据,并把数据按分区方式送到数据锁存器组锁存。锁存器输出16分区数据,通过移位寄存器组实现并串转换得到显示屏所需要的串行数据,并送往LED显示屏列驱动电路。脉冲发生器为各模块提供相应的同步时钟,行地址发生器产生相应的行信号送往显示屏的行驱动电路。

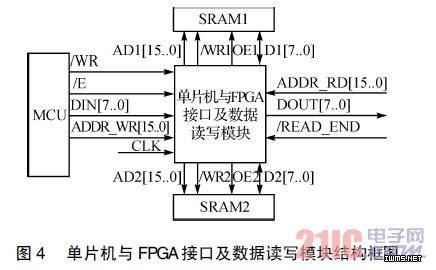

3.2 单片机与FPGA接口及数据读写模块

单片机与FPGA接口及数据读写模块结构如图4所示。单片机从EEPROM中读取数据并根据显示要求进行处理后,通过接口及数据读写模块把数据送往数据缓冲器SRAM1或SRAM2。为提高数据的传输速度,保证显示效果的连续性,在系统中采用双体切换技术来完成数据存储过程。也就是说,采用双SRAM存储结构,两套完全独立的读、写地址线和数据线轮流切换进行读写。工作时,FPGA在一个特定的时间只从两块SRAM中的一块读取显示的数据进行显示,同时另外一块SRAM与MCU进行数据交换。MCU会写入新的数据,依次交替工作,可实现左移、上移、双屏等显示模式。如果显示的内容不改变,即一块SRAM里的数据不变时,MCU不需要给另外一块SRAM写数据。

该模块采用VHDL有限状态机来实现,整个控制分为4个状态,其状态转换图如图5所示。其工作过程如下: