・上一文章:最新全能数控电源IC-ADP1043A(二)

・下一文章:基于LJDZN8400T的智能触摸液晶显示终端控制系统

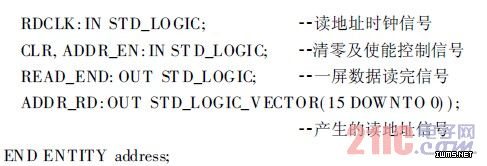

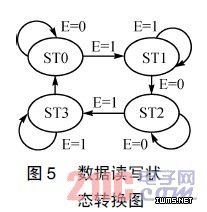

系统开机进入初始状态ST0,单片机的写入使能端E为低电平,单片机从EEPROM中读取数据并把数据写入到SRAM1,同时FPGA读取SRAM2中的数据;当单片机数据写完一屏数据后E变为高电平,当FPGA从SRAM2中读完数据、结束信号READ_END为低电平时,进入ST1状态。

在ST1状态下,若没有新的数据写入则E保持高电平,FPGA读取SRAM1的数据,为静态显示;只有当单片机的读入控制信号E为低电平且READ_END为低电平时,进入ST2状态。在ST2状态下,单片机把数据写入SRAM2,同时FPGA读取SRAM1的数据,单片机数据写完后E变为高电平,当FPGA一屏数据读完后READ_END为低电平,进入ST3状态。在ST3状态下,如果没有新数据写入E为高电平,FPGA读取SRAM2中的数据。当单片机有新的数据写入时E变为低电平,当FPGA一屏数据读完后READ_END为低电平时,重新进入ST0状态。通过这种周而复始的交替工作完成数据的写入与读取,其端口程序如下:

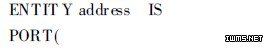

3.3 读地址发生器

读地址发生器主要产生外部缓存器SRAM1(SRAM2)的读地址信号,使系统能正确地从存储器中读取相应的显示数据。其地址最高位为0,其余地址分别为行地址(hang[30])、列地址(lie[60])、分区地址(qu[30])15位有效地址信号。在16个脉冲周期内读出在SRAM1(SRAM2)中的16字节数据,其部分VHDL源程序如下: