当PC机需要通过PXIE总线发送数据时,首先PC机为DMA传输在内存中划定两块内存空间,作为数据的第一级缓存,并将这两块内存空间的基地址和大小轮流通过PXIE总线传给DMA控制器。这些配置命令通过特定的字符串被识别,并写入相应的配置命令寄存器。划定两块内存空间是为了在当DMA控制器从一块内存中读取数据时,PC机可以向另一块内存写入数据,以乒乓操作的形式提高传输效率。

接下来,PC机发起对数据的传输。PC机上的PCIe控制器从内存中取得数据后,将原始数据封装,并串转换往下继续传输,数据包通过吉比特串行收发器传至FPGA,在进入PCIe IP核后被拆解,剥离的纠错信息作为包进一步处理的依据,最后在应用层以并行数据的形式推入DMA控制器。

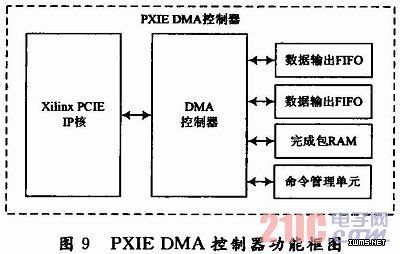

DMA控制器将数据流存人数据输出FIFO,根据FIFO剩余空间的大小判定是否从PC机中继续读取数据,这样就保证了数据不会因为来不及从FIFO中取走而丢失。当DMA控制器接收到一块内存大小的数据之后,就会以边带信号的形式发送中断信号给上位机,上位机接收到中断之后就可以开始下1次DMA传输。

当PC机需要通过PXIE总线接收数据时,工作流程与通过PXIE总线发送数据基本类似,主要区别在于从PC机往下发送的包里不包含数据,仅包含路由及其他控制信息,DMA控制器接收到包后,会以完成包的形式将数据打包往上传回PC机,完成包按照接收到包中的路由信息,逆向寻址回到PC机的内存,PC机就完成了一次通过PXIE总线接收数据。

加入DMA控制器之后的PXIE总线被重新封装,操作得到简化。

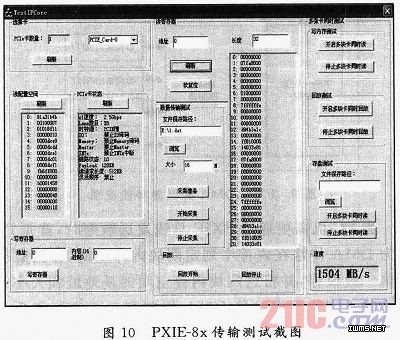

2.3 测试结果

在测试中,PXIE配置为8通道,测试数据为16 MB,在PC机通过PXIE接口读取数据的操作过程当中,平均数据率达到1 504 Mb/s。在PC机通过PXIE接口发送数据的操作过程中,平均数据率达到1 490 Mb/s。通过PCIe测速软件进行传输速度测试,其结果如图10所示。

3 结语

本文介绍了一种基于PXIE总线和Camera Link协议的高速CCD图像采集系统的设计方案。该方案给出了一种Camera Link硬件接口电路的设计思路,并且选用Xilinx公司的Virtex-5 LX50T型FPGA作为整个采集系统的核心处理器,同时对Virtex-5自带的IPcore进行研究和开发,实现Camera Link采集卡通过PXIE总线与上位机进行串行通信。在试验过程中,FPGA设计灵活,开发周期短的优点充分得以体现,为下一步的高速图像采集系统的研制奠定了基础。